- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: KEA ADC overrun misaligns internal FIFO

KEA ADC overrun misaligns internal FIFO

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

KEA ADC overrun misaligns internal FIFO

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

In order to evaluate the ADC of this MCU I wrote a simple test software to continuously read out one ADC channel (see attachment “main.c”).

I use the FIFO feature of the ADC to always get 8 samples at once per ISR call.

Actually this code works well as long as no overrun occurs in the ADC FIFO (or in other words, as long as I always read the “ADC_R” register before the next ADC sample is available).

But if for some reason I lose at least one ADC sample (FIFO overrun occurs, for example due to a higher priority ISR), the FIFO seems to be out of sync for all future reads. So from this time on, I always get the 8 ADC samples in a wrong order when reading the “ADC_R” register.

The datasheet says that if FIFO is full, then the next conversion will override old data in case of no read action.

This is fine, but it seems then that the internal FIFO pointer has been shifted even for the next interrupts...

---

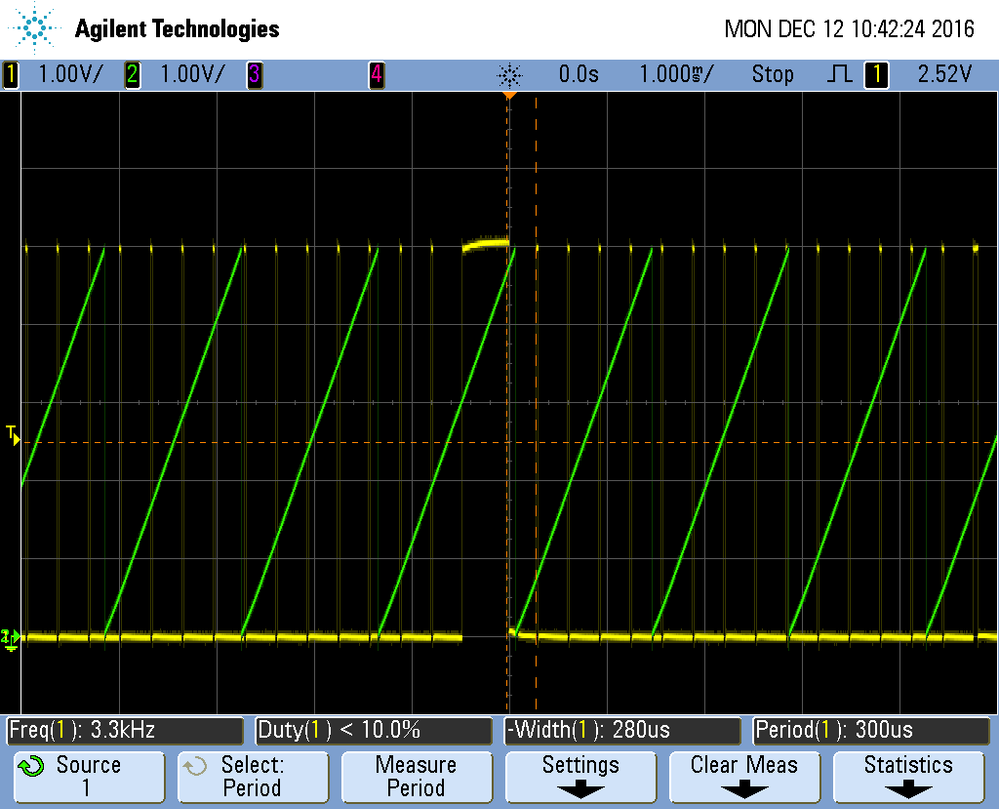

For better understanding, I have attached some pictures of my measurement:

- “scope_1.png” shows the signals on the MCU pins PTC0 (AD8) and PTE0 (“SCOPE_PIN” in the sample code)

- Green line: Waveform on the ADC input pin (sawtooth from a waveform generator)

- Yellow line: Activity of the ADC ISR (low = background task, high = ISR processing).

- “values_1.png” shows the measured ADC values

- Gray bars: Count of ADC values fetched in the ISR (array “adc_count_buffer”)

- Red dots: Measured ADC values (array “adc_buffer” which was filled by reading the FIFO register “ADC_R”)

As you can see, I have simulated a FIFO overrun in the middle of the measurement with a short busy wait in the ADC ISR. Before this overrun, all ADC values are correct, but after it the order of the ADC samples is wrong. This makes it impossible to design a robust and reliable firmware, because losing one single ADC sample can lead to permanently wrong ADC results in future.

Do you have an idea what’s going wrong here and how I can avoid this?

Thanks in advance,

BR,

Philippe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This definitely looks like a hardware bug.

The oldest conversion gets overwritten by the new conversion, but the front of the FIFO does not get updated.

To avoid this you probably have to set the ADC as the highest priority interrupt.

Alternatively you can try to use the DMA to transfer the FIFO ta a local buffer.

If those are not feasible and you don't mind losing samples you need to check the overrun flag each time the FIFO is going to be read and empty it if the overrun flag is set.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ricardo,

It is included in the zip file I have sent you by mail.

Anyway, here is it.

BR,

Philippe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

This issue looks like a hardware bug in the FIFO?

Can confirm this?

BR,

Philippe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Phil,

could you please share your main.c file, is not attached in thread.

thanks!

regards,

Ricardo Olivares

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Any feedback?

BR,

Philippe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Unfortunately the ASCANE bit did not change anything, so the problem still exists.

And detecting an overrun is not possible (unexpected interrupt can arrive anytime), so I don’t know when I have to reset the FIFO...

Do you have any other recommandation ?

BR,

Philippe.

Note : I insert the 2 screeshot that you could not read.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Can you set the ASCANE bit in ADC_SC4 register and have a try? If you set the bit, the FIFO always use the first dummied FIFO channels when it is enabled.

If the above method can not fix the issue, as a workaround, you can write 0x1F to ADCH bits in ADC_SC1 register to reset the FIFO when overrun event happens.

BTW, I can not see the scope_1.png and values_1.png you submitted.

Hope it can help you.

BR

XiangJun Rong