- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- K82: access to SRF and VBAT register files with User privileges

K82: access to SRF and VBAT register files with User privileges

K82: access to SRF and VBAT register files with User privileges

Hi !

Do I undestand right :

- VBAT and SR addresses window spaces mapped to AIPSx bridge areas directly

- As result access to VBAT&SR can't be protected by MPU or AIPSx bridge settings

and it is possible to access to those spaces in User execution mode ( And Supervisor as well ) ?

- for enable access to VBAT & SR , bit29 ( RTC access control bit ) should be enabled in SIM_SCGC6 register ?

Looks like no any dependencies to RTC clock and line CLOCK_EnableClock(kCLOCK_Rtc0) is not mandatory

for read/write to those Register Files. And there are keep values over reboot operation.

But access with User priviliges cause BusFault.

How ro activate AIPSx type of restriction to those areas and have access with User privileges and able to write protect it from Supervisor accesses ?

Regards,

Eugene

Hi Eugene Hiihtaja

According to Reference Manual:

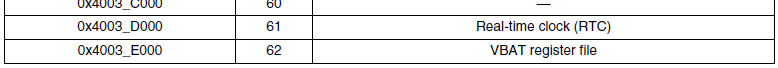

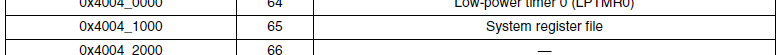

Both VBAT register file and System register file have a slot number, so you can grant different access levels with the slot number in the AIPSx_PACRn register.

for enable access to VBAT & SR, bit29 ( RTC access control bit ) should be enabled in SIM_SCGC6 register ?.

No, there is no dependency in the RTC and the register files.

Hope this helps

Regards

Hi Antonio !

For access to register files I'm using address space definitions :

/* System Register File ( 32 bytes , 8 dwords ) base address */

#define SRF_BASE (0x40041000U)

/* SRF base pointer */

#define SRF ((volatile uint32_t *)SRF_BASE)

/* VBAT Register File ( 128 bytes, 32 dwords) base address */

#define VBATRF_BASE (0x4003E000U)

/* VBATRF base pointer */

#define VBATRF ((volatile uint32_t *)VBATRF_BASE)

It means AIPSx registers are the same as real address space of register files ?

Or first 32bit register is reserved for AIPS slot and after that register file is allocated ?

Regards,

Eugene