- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Help with Flexbus example on TWR-K53N512

Help with Flexbus example on TWR-K53N512

Help with Flexbus example on TWR-K53N512

Hi All,

I've been attempting to attach a 16-bit parallel TFT display to my TWR-K53N512 TWR board via the Flexbus and I've been having issues. First with my D/C line not getting set and cleared correctly; and now no activity on my AD[0]-[15] lines. I was hoping someone can point me in the right direction.

Some background notes:

- I'm heavily using the application note "Using FlexBus Interface for Kinetis Microcontrollers" as a reference(pg 14 LCD). Since this app note uses the K60, I've had to do some pin remapping for the k53.

- The display I'm using is a cfaf240320k024tts TFT Display, It pretty accurately functions the same as the one in the app note.

- I'm using a USBee AX logic analyzer to probe lines

- I've attached all relevant links at the end of the post

- I'm using KDS v3.0

- Since i'm using the TWR-K53N512 and KDS, I had to download The MK53DN512 SDK from mcuxpresso SDK Builder for register includes(Specifically #include <MK53D10.h>)

- I've attached my code below

- I haven't posted to the NXP fourms often so please feel free to let me know if I need to move the post to the appropriate area

Questions:

- I can't get my D/C line(FB_ad[16]) to toggle when i'm trying to send a command vs data.

- Oddly enough after poking around I found a signal that looks like what it is supposed to be but it is on FB_AD[18] instead of FB_AD[16]. Why is this not on 16 or what is this signal?

- In general does anything look wrong in the code? I originally only had the issue with my D/C line, but now I can't get any activity on my AD[0]-[15] lines. I've attempted to revert back to a working version but I still can't get anything from them except a few 1-0 or 0-1 random transitions.

- How does setting CMSR0[BAM] define the block size?

- In the example "Using FlexBus Interface for Kinetis Microcontrollers", They state that:

Setting the base address mask to 1 (CSMR0[BAM]) = 1) means that the block size for the CS is 2^n (n = number of bits in CSMR[BAM] + 16) must be 128 KB. This means address 0x60000000 to 0x6001FFFF can be accessed by the CS. Therefore address 0x6000000 (FB_AD16 is low) can be used to access the index register of the SSD1289, and address 0x60010000 (FB_AD16 is high) can be used to access the data buffer of the SSD1289.

- So in this example: n = 1 + 16, so n^17 = 131072(round to 128KB) which makes sense.

- However, Where are they getting this information? I can't find it listed anywhere in the reference manual. Is this the same for the K53?

- In the example "Using FlexBus Interface for Kinetis Microcontrollers", They state that:

- How do you set the system clock (or MCGOUTCLK)?

- When Setting the Flexbus clock I understand that it has to be under 50MHz by design but also slower than my Clock cycle time on my display. In the case of my display it is 120ns, which means it has to be 32MHz or slower for it to write properly. I found that In order to get 32MHz, i need get the system clock at 96MHz and then set the following:

#define FLEX_CLK_INIT SIM_CLKDIV1_OUTDIV3(2)// FlexBus = Sysclk/3 pg314 SIM->CLKDIV1 |= FLEX_CLK_INIT;- The problem is I'm sure exactly how to set MCGOUTCLK. I know i have to choose either the PLL or FLL and multiply an oscillator by a value but I'm a little lost on what registers i need to write to.

- For register FB_CSCR0[PS], What is the difference between between setting as 0x2 vs 0x3? They both seem to set 16-bit port sizes.

- Why does KDS force you to refrence registers via structure and not directly like below?

- SIM_SOPT2 |= SIM_SOPT2_FBSL(3)

Links:

- Using FlexBus Interface for Kinetis Microcontrollers

- K60 Sub Family Reference Manual

- K53 Sub Family Reference Manual

- TWR-K60 Schematic

- TWR-K53 Schematic (Actually having a hard time searching the NXP site for a link to the schematic. I attached a copy i had locally).

- TWR-K53N512 Tower page on NXP

Code:

#include <MK53D10.h>

void flexinit(void);

void vfnSendDataWord(unsigned short value);

void vfnSendCmdWord(unsigned short cmd);

#define ALT5 (PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK) // Alternative function 5 = FB enable pg279

#define ALT1 (PORT_PCR_MUX(1)|PORT_PCR_DSE_MASK) // Alternative function 1 = GPIO pg279

#define FLEX_CLK_INIT SIM_CLKDIV1_OUTDIV3(3)// FlexBus = Sysclk/2 pg314

//#define FLEX_CLK_INIT (SIM_CLKDIV1 |=CLKDIV1 SIM_CLKDIV1_OUTDIV3(1))// FlexBus = Sysclk/2 pg314

void flexinit(void){

//SIM_SCGC5 System clock gating control Register 5 pg.309

//Enables clocks for all ports

SIM->SCGC5 |= SIM_SCGC5_PORTA_MASK | SIM_SCGC5_PORTB_MASK | SIM_SCGC5_PORTC_MASK | SIM_SCGC5_PORTD_MASK | SIM_SCGC5_PORTE_MASK;

SIM->CLKDIV1 |= FLEX_CLK_INIT;

/* These are the K60 pinouts

* PORTC_PCR9=ALT5;

PORTC_PCR10=ALT5;

PORTC_PCR11=ALT5;

PORTD_PCR1=ALT5;

PORTD_PCR2=ALT5;

PORTD_PCR3=ALT5;

PORTD_PCR4=ALT5;

PORTD_PCR5=ALT5;

PORTD_PCR6=ALT5;

PORTB_PCR17=ALT5;

PORTB_PCR18=ALT5;

PORTC_PCR0=ALT5;

PORTC_PCR1=ALT5;

PORTC_PCR2=ALT5;

PORTC_PCR3=ALT5;

PORTC_PCR4=ALT5;

PORTC_PCR5=ALT5;

PORTC_PCR6=ALT5;

PORTC_PCR7=ALT5;

PORTC_PCR8=ALT5; */

//Change them to TWR-K53 Pinouts

//Data Lines

PORTA->PCR[10]=ALT5; //EBI_AD15

PORTA->PCR[24]=ALT5; //EBI_AD14

PORTA->PCR[25]=ALT5; //EBI_AD13

PORTA->PCR[26]=ALT5; //EBI_AD12

PORTA->PCR[27]=ALT5; //EBI_AD11

PORTA->PCR[28]=ALT5; //EBI_AD10

PORTD->PCR[10]=ALT5; //EBI_AD9

PORTD->PCR[11]=ALT5; //EBI_AD8

PORTD->PCR[12]=ALT5; //EBI_AD7

PORTD->PCR[13]=ALT5; //EBI_AD6

PORTD->PCR[14]=ALT5; //EBI_AD5

PORTE->PCR[8]=ALT5; //EBI_AD4

PORTE->PCR[9]=ALT5; //EBI_AD3

PORTE->PCR[10]=ALT5; //EBI_AD2

PORTE->PCR[11]=ALT5; //EBI_AD1

PORTE->PCR[12]=ALT5; //EBI_AD0

//Control Lines

PORTA->PCR[6]=ALT5; //CLKOUT0

PORTD->PCR[15]=ALT5; //EBI_R/W

PORTE->PCR[7]=ALT5; //EBI_CS0_B

PORTA->PCR[9]=ALT5; //EBI_AD16

//Reset pin not on FB

PORTD->PCR[4]=ALT1; //Set as GPIO

GPIOD->PDDR = 0x10; //Set as output

//SIM_SOPT2 is the System Options Register 2 Pg 292

//Flexbus security level set to 11; off-chip instruction accesses and data accesses are allowed

SIM->SOPT2 |= SIM_SOPT2_FBSL(3);

//SIM_SCGC7 is the System clock gating control register 7 pg313

//Sets the Flexbus clock to enabled

SIM->SCGC7 |= SIM_SCGC7_FLEXBUS_MASK;

#define FLEX_DC_ADDRESS 0x60000000

#define FLEX_BASE_ADDRESS 0x60010000

#define FLEX_ADRESS_MASK 0x00010000

FB->CS[0].CSAR = FLEX_DC_ADDRESS; // CS0 base address

#define FLEX_CSMR_V_MASK FB_CSMR_V_MASK //0x1U

FB->CS[0].CSMR = FLEX_ADRESS_MASK | FB_CSMR_V_MASK; // The address range is set to 128K because the DC signal is connected on address wire

// MUX mode + Wait States

#define FLEX_CSCR_MUX_MASK (FB_CSCR_BLS_MASK) //Sets the BLS to right-aligned (0x200U)

#define FLEX_CSCR_AA_MASK FB_CSCR_AA_MASK //Sets the AA to Enable (0x100U)

#define FLEX_CSCR_PS1_MASK (FB_CSCR_PS(2)) //Sets the Port Size to 16bit (0x080U) //(((uint32_t)(((uint32_t)(x)) << FB_CSCR_PS_SHIFT)) & FB_CSCR_PS_MASK)

FB->CS[0].CSCR = FLEX_CSCR_MUX_MASK | FLEX_CSCR_AA_MASK | FLEX_CSCR_PS1_MASK; // FlexBus setup as fast as possible in multiplexed mode

}

void vfnSendDataWord(unsigned short value)

{

*((unsigned short*)FLEX_BASE_ADDRESS) = value;

}

void vfnSendCmdWord(unsigned short cmd)

{

*((unsigned short*)FLEX_DC_ADDRESS) = cmd;

}

int main(void) {

/* Init board hardware. */

//BOARD_InitPins();

//BOARD_BootClockRUN();

//BOARD_InitDebugConsole();

flexinit();

for(;;) { /* Infinite loop to avoid leaving the main function */

//Check to see if each individual bit is working

vfnSendCmdWord(0x0000);

vfnSendDataWord(0x0001);

vfnSendDataWord(0x0002);

vfnSendDataWord(0x0004);

vfnSendDataWord(0x0008);

vfnSendDataWord(0x0010);

vfnSendDataWord(0x0020);

vfnSendDataWord(0x0040);

vfnSendDataWord(0x0080);

vfnSendDataWord(0x0100);

vfnSendDataWord(0x0200);

vfnSendDataWord(0x0400);

vfnSendDataWord(0x0800);

vfnSendDataWord(0x1000);

vfnSendDataWord(0x2000);

vfnSendDataWord(0x4000);

vfnSendDataWord(0x8000);

__asm("NOP"); /* something to use as a breakpoint stop while looping */

}

}Thanks for any help and time,

Paul

Hi Paul

This is the K53 TFT configuration in the uTasker project:

#define GLCD_COMMAND_ADDR 0x60400000

#define GLCD_DATA_ADDR 0x60410000

_CONFIG_PERIPHERAL(A, 9, (PA_9_FB_AD16 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(A, 10, (PA_10_FB_AD15 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(A, 24, (PA_24_FB_AD14 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(A, 25, (PA_25_FB_AD13 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(A, 26, (PA_26_FB_AD12 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(A, 27, (PA_27_FB_AD11 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(A, 28, (PA_28_FB_AD10 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(D, 10, (PD_10_FB_AD9 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(D, 11, (PD_11_FB_AD8 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(D, 12, (PD_12_FB_AD7 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(D, 13, (PD_13_FB_AD6 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(D, 14, (PD_14_FB_AD5 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(E, 8, (PE_8_FB_AD4 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(E, 9, (PE_9_FB_AD3 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(E, 10, (PE_10_FB_AD2 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(E, 11, (PE_11_FB_AD1 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(E, 12, (PE_12_FB_AD0 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(E, 7, (PE_7_FB_CS0 | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

_CONFIG_PERIPHERAL(D, 15, (PD_15_FB_RW | PORT_DSE_HIGH | PORT_PS_DOWN_ENABLE));

CSAR0 = GLCD_COMMAND_ADDR; \

CSMR0 = (0x00010000 | FB_CS_VALID); \

CSCR0 = (FB_BLS | FB_AA | PORT_SIZE_16);

I didn't spot any differences.

- Note that CSCR0 PS value of 2 is the 16 bit setting. A setting of 3 may work but such a setting is not defined as a valid one and so should be avoided.

- Block size is set by 0x00010000 in SMSR0 - matching the command/address setting where FB_AD16 is then used as command/data selection.

- The FlexBus clock is derived from the core clock divided by the value in CLKDIV1 (DIV3) as you have shown - see the uTasker simulator output below which emulates the K53 and a TFT and also displays the clock values that the code is setting. Its pin emulator displays the selected MUX values so that this can be checked (example of hovering the mouse over the PTD10 (the FB_AD9 function)

Regards

Mark

uTasker GLCD library with Kinetis and Display simulation: http://www.utasker.com/docs/uTasker/uTaskerLCD.PDF

Videos: https://youtu.be/AdtRyQ-2IrE / https://youtu.be/2Rbz1SOoJVI

uTasker developer and supporter (+5'000 hours experience on +60 Kinetis derivatives in +80 product developments)

Kinetis: http://www.utasker.com/kinetis.html

Hi Mark,

Thanks for the quick response. I've started looking into uTasker and it looks like it will be really helpful.

I think I found out why all my lines recently went haywire. I currently have a TWR-K53N512 board attached to the TWR-ELV modules and my TFT display attached to the Primary Elevator via 2mm to 2.54mm jumper cables. I recently decided to do a continuity check to make sure some data lines weren't touching and found that lines A80-73 on the Primary elevator were connected somehow. I began probing around more and started disconnecting my entire setup. It seems that with the power on and nothing connected but the K53 and the Elevator modules, A80-73 is connected and my 5V bus is showing continuity with ground and so is my 3.3v bus(Not great). I moved further up to just have only the K53 and I checked if PE11 and PE12 were connected somewhere on the board. This lead me to check pin 2,3 and 6 on the J2 header but found that these were not showing continuity at all.

So right now i'm at a loss of what parts may be possibly broken. The board seems like it still programs/debugs fine. Do you have any suggestions on what points to probe to tell if my K53 or my Elevator modules are dead?

Thanks again,

Paul

Hi Paul

I have a few tower kits and one of them had a back-plane/elevator with a break in a bus connection (internally) which I needed to correct by soldering a wire in parallel to.

As with all HW there can be a fault but I don't have a suggestion as to where to actually check.

The best thing to do is use a logic analyser to check the complete bus timing since you will then immediately see if something is stuck (due to short circuit, open circuit or setup error).

If you don't have this possibility I would load code that toggles all of the signals that are to be used (in GPIO mode) so that you can check that each one is arriving at its destination using a single scope channel (and if the voltage swing is not good it will also be seen). It is best if you can individually turn then on and off as desired so that you can be sure that you are measuring the one of interest and not one shorted to another line, etc.

Good luck

Regards

Mark

Hi Mark,

Sorry about the later response and thanks for your suggestions.

I've actually had some time recently to poke at my TWR-K53 board and I've notice a few things.

- I have loaded essentially a blank project to the board and I still get continuity between FB_AD[0] -> FB_AD8(Pins 80-73 on the Primary Elevator).

- After this I figured I should find a way to test this without the TWR-ELV in the mix so I took them off and I started probing points directly on the board with the power still on.

- I first wanted to test if the 5v and 3v3 supplies were good. I used TP2 for the 5v, TP11 for the GND and TP7 for the 3v3 check. They all seems to register at correct supply values. So that seems good at least.

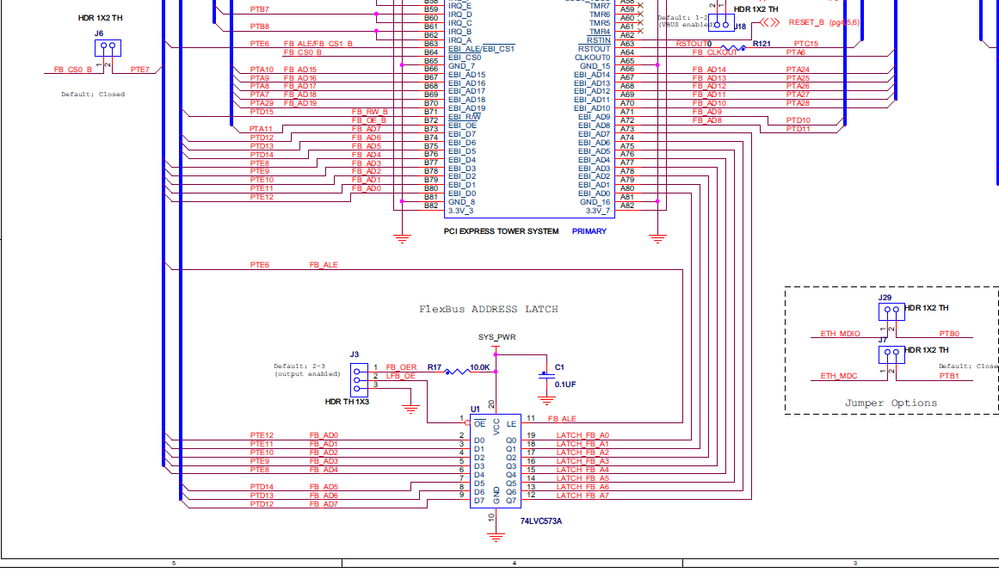

- Next i moved onto the Flexbus lines. I tested the lines directly at the Flexbus Address Latch(U1 in the image below). It turns out that if I probe the LATCH_FB[0] to LATCH_FB[7] , they are all connected but the MCU side of the latch is totally fine.

- Does this mean that my address latch is probably blown and I need to replace it? I looked into the data sheet and I can't find a situation where all of the outputs would be connected. Suggestions?

Thank you again for your time and help,

Paul

Hi Paul

if the lines are shorted together there must be something wrong.

You don't need the latch in your circuit so you could just remove it and connect the inputs to the outputs if you are certain that there is a problem with the chip.

Regards

Mark