- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- FRDM-KL02Z Power Modes drawing too much current

FRDM-KL02Z Power Modes drawing too much current

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

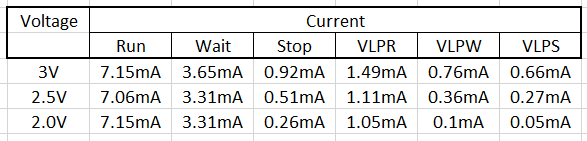

I have a FRDM-KL02Z board which seems to be drawing a much higher current than stated on the data sheet. I am testing the current across the header J4 on the board, with resistors R27 and R32 removed from the board. In order to remove any issues that may come from my own code I've tested the board using the "power_mode_switch" demo app from the nxp website, and interfacing with the board using UART pins on header J8 instead of via openSDA. The headers J5 and J11 have been disconnected with R31 and R28 also being removed from the board.

The results I've recorded seem to be much higher than the documentation suggests, especially in the very low power modes. Any suggestions on what I can try in order to bring the current draw down?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The external voltage of UART pins will affect the current.

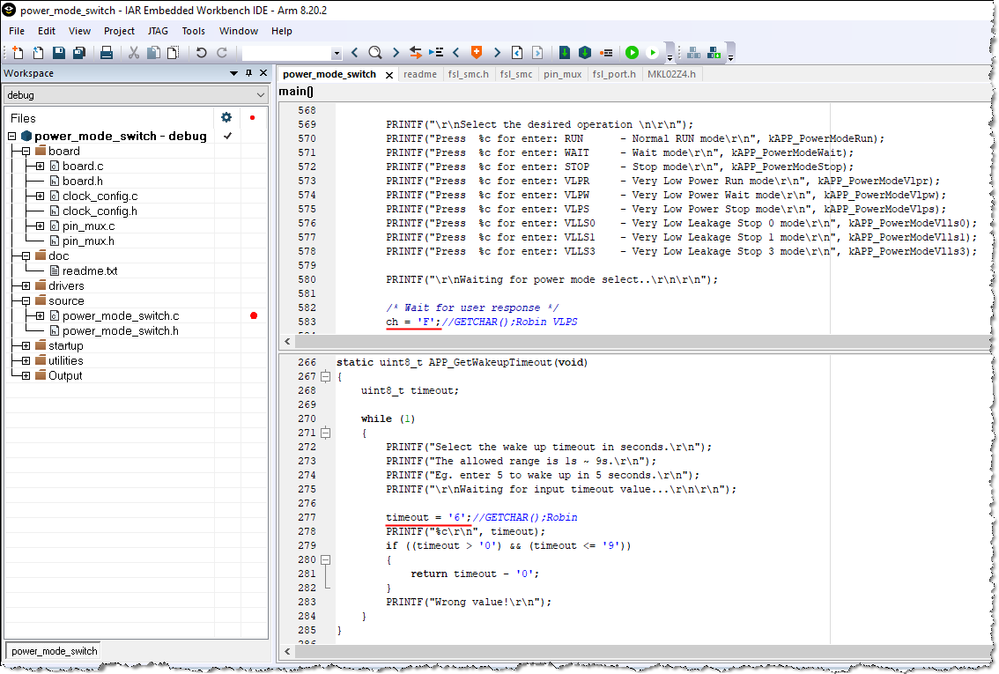

You can select VLPS mode by modify the codes shown below:

I did not remove J5 \J11\R31 \R28, I can get 2uA in VLPS mode. The OpenSDA firmware has attached.

You can also try to remove the R16 and R17.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The external voltage of UART pins will affect the current.

You can select VLPS mode by modify the codes shown below:

I did not remove J5 \J11\R31 \R28, I can get 2uA in VLPS mode. The OpenSDA firmware has attached.

You can also try to remove the R16 and R17.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It looks like the way I'd setup up the headers stopped things from working correctly. The UART connection was also having a big effect on the board. Cheers for the help!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ben

If using UARTs make sure that the pins are not floating (valid for all GPIO) since that causes high leakage.

Some low power links:

Low power and LLWU: http://www.utasker.com/kinetis/LLWU.html

Low power videos:

- https://youtu.be/kWNlsAoMly4

- https://youtu.be/iZEMRiDmHzw

- https://youtu.be/v4UnfcDiaE4

VLPS with continuous UART operation: https://community.nxp.com/message/421247#421247

Reference binary for FRDM-KL02Z with dynamic low power operation: http://www.utasker.com/kinetis/FRDM-KL02Z.html

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Also, I forgot to mention that the voltage for the tests is being supplied through the coin cell holder BT1.