- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- FRDM-K66F, MCG and 12MHz.

FRDM-K66F, MCG and 12MHz.

Hi

12MHz crystal can be used for 180MHz operation (in HSRUN mode).

http://www.utasker.com/kinetis/MCG.html

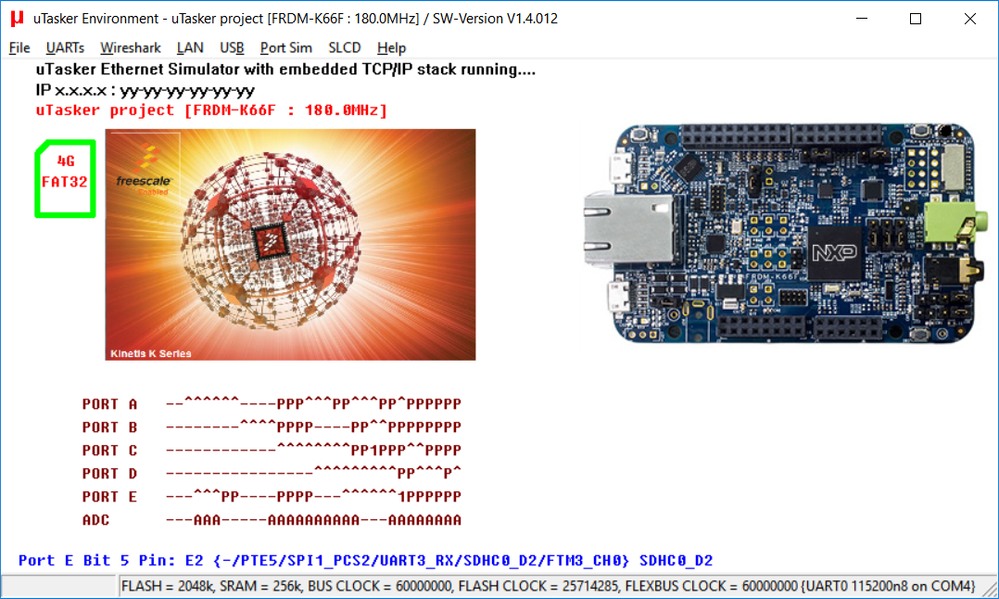

See below (simulation of K66 board) with the following settings:

#define CRYSTAL_FREQUENCY 12000000 // 12 MHz crystal

#define CLOCK_DIV 1 // input must be divided to 8MHz..16MHz range (/1 to /8)

#define CLOCK_MUL 30 // the PLL multiplication factor to achieve operating frequency of 180MHz (x16 to x47 possible) [PLL output range 90..180MHz - VCO is PLL * 2]

#define BUS_CLOCK_DIVIDE 3 // 180/3 to give 60MHz (max. 60MHz)

#define FLEX_CLOCK_DIVIDE 3 // 180/3 to give 60MHz (max. 60MHz)

#define FLASH_CLOCK_DIVIDE 7 // 180/7 to give 25.714MHz (max. 28MHz)

Beware of restrictions in HSRUN mode - for example flash programming is not possible.

Regards

Mark

Thank you Mark Butcher,

This and your advice at "MK66 180 Mhz, how config clock with Config Tools " has sorted thing out. Some things to mention/ponder...

1) Unlike my code your code did not hang at IREFST. The difference was you do not set HGO.

2) I found that 180MHz runs without setting RUNHS. I'm presuming while this is possible, it only when RUNHS is set that 180MHz is guaranteed.

3) Wonder if the Flash issue is because of the elevated voltage in RUNHS mode.

Anyway, thank you,

Hi

Yes it is possible to run at 180MHz in RUN mode (without Flash programming restrictions) but it is not using the processor within its guaranteed specification (over-clocking). It is OK to do this in a hobby project but would not be acceptable in a serious product development and negligent in some products (especially anything that required high reliability or were safety critical in any respects).

Regards

Mark

Hi

12MHz crystal can be used for 180MHz operation (in HSRUN mode).

http://www.utasker.com/kinetis/MCG.html

See below (simulation of K66 board) with the following settings:

#define CRYSTAL_FREQUENCY 12000000 // 12 MHz crystal

#define CLOCK_DIV 1 // input must be divided to 8MHz..16MHz range (/1 to /8)

#define CLOCK_MUL 30 // the PLL multiplication factor to achieve operating frequency of 180MHz (x16 to x47 possible) [PLL output range 90..180MHz - VCO is PLL * 2]

#define BUS_CLOCK_DIVIDE 3 // 180/3 to give 60MHz (max. 60MHz)

#define FLEX_CLOCK_DIVIDE 3 // 180/3 to give 60MHz (max. 60MHz)

#define FLASH_CLOCK_DIVIDE 7 // 180/7 to give 25.714MHz (max. 28MHz)

Beware of restrictions in HSRUN mode - for example flash programming is not possible.

Regards

Mark