- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: Achieving maximum ADC conversion rate

Achieving maximum ADC conversion rate

Hello,

I'm using Kinetis Design Studio 3.0.0 for the controller MK02FN128VFM10. I'm using 16 bit differential configuration for ADC for my project.

As mentioned in the datasheet, with no hardware averaging, maximum ADC conversion rate of 461 KSamples per second can be attained. But in my case, with this specification I'm getting 90 KSamples per second.

So how to achieve the maximum ADC conversion rate?

Also, in the datasheet, 'To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.' is mentioned. These settings are already done, so according to it maximum ADC conversion clock frequency is in operation.

How to tackle with this issue? Please help.

Reply awaited.

已解决! 转到解答。

Hi,

yes, it is pretty simple. If the bus is 40MHz then just look at the ADC clock divider (ADIV) and ADC input clock (ADICLK) then ADCCLK = ADICLK/ADIV.

NOTE: if 40MHz bus lcok is selected, and ADC input lock is BUSCLK then you will not get the best conversion speed, as for maximum speed ADCCLK need to be 12MHz. The is not integer divider for 40MHz which will results in 12MHz.

regards

R.

Hello,

there are not enough of information in your message.

BUS clk?

ADC clk?

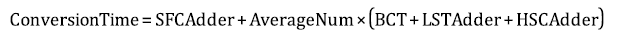

SFCAdder = 5 cycles of ADCCLK + 5 BUSCLK

averaging = disabled (1 average number factor)

high speed mode = enabled (2 cycles ADCCLK)

converison mode = 16 bits and differencial mode = enabled (34 cycles ADCCLK base conversion time BCT)

sample time = shortest (0 cycles of ADCCLK)

If I will consider peripheral bus clock BUSCLK = 48MHz divided by 4 to get ADCCLK = 12MHz then:

ConversionTime = 5*(1/12000000)+5*(1/48000000)+1*(34+0+2)*(1/12000000)=~3.52us -> ~284kSamples

What you can see in datasheet is the value of single-ended channel.

However, consider that with such configuration the resulting accuracy will be lower. i do not recommend to measure a signals with higher external impedance. This should be minimazes as possible. The based way is supply the ADC input from OA output (follower circuit).

regards

R.

Hi,

yes, it is pretty simple. If the bus is 40MHz then just look at the ADC clock divider (ADIV) and ADC input clock (ADICLK) then ADCCLK = ADICLK/ADIV.

NOTE: if 40MHz bus lcok is selected, and ADC input lock is BUSCLK then you will not get the best conversion speed, as for maximum speed ADCCLK need to be 12MHz. The is not integer divider for 40MHz which will results in 12MHz.

regards

R.