- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Access to peripherals in UserMode when K82 MPU is enabled

Access to peripherals in UserMode when K82 MPU is enabled

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi !

It is not so clear from documentation if K82 MPU can be configured for access to simple peripherals (LPUART0 )

in UserMode. All trials to configure LPUART address space in MPU for read/write space dosn't have any effect and simple read of DATA register cause BusFault.

Not all ARM can grant access for this area in UserMode.

But what about K82 ?

Does it possible to configure K82 MPU if in UserMode to have access to LPUART0 and i2C address space ?

Regards,

Eugene

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Xiangjun Rong !

Thank you ! It is really work like this. It have sense to add AIPS table to each TCB of FreeRTOS for get more secure execution environment.

I have few small questions about K82 after that.

1. So it is dosn't have sense to protect by MPU areas after 0x40000000 where peripherals starts ?

Core always have access to this area and only AIPS0/AIPS1 blocks can be used for protect peripheral memory mapped area ?

2. Private Peripherals at address >= 0xE00000000 is always accessible by core in privileged mode and MPU settings dosn't have any effect as well.

By the way , do you have any application note where all peripherals what have effect to security is explained for K82 ?

What should be hardened for get from K82 as max protection as possible ?

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Xiangjun Rong !

Thank you ! It is really work like this. It have sense to add AIPS table to each TCB of FreeRTOS for get more secure execution environment.

I have few small questions about K82 after that.

1. So it is dosn't have sense to protect by MPU areas after 0x40000000 where peripherals starts ?

Core always have access to this area and only AIPS0/AIPS1 blocks can be used for protect peripheral memory mapped area ?

2. Private Peripherals at address >= 0xE00000000 is always accessible by core in privileged mode and MPU settings dosn't have any effect as well.

By the way , do you have any application note where all peripherals what have effect to security is explained for K82 ?

What should be hardened for get from K82 as max protection as possible ?

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Eugene,

I think the MPU module is used to protect memory rather than the peripheral as the name MPU implies "memory protection unit".

If you access the peripheral, you can set the AIPSx_PACRn and AIPSx_MPRA register to protect the peripheral.

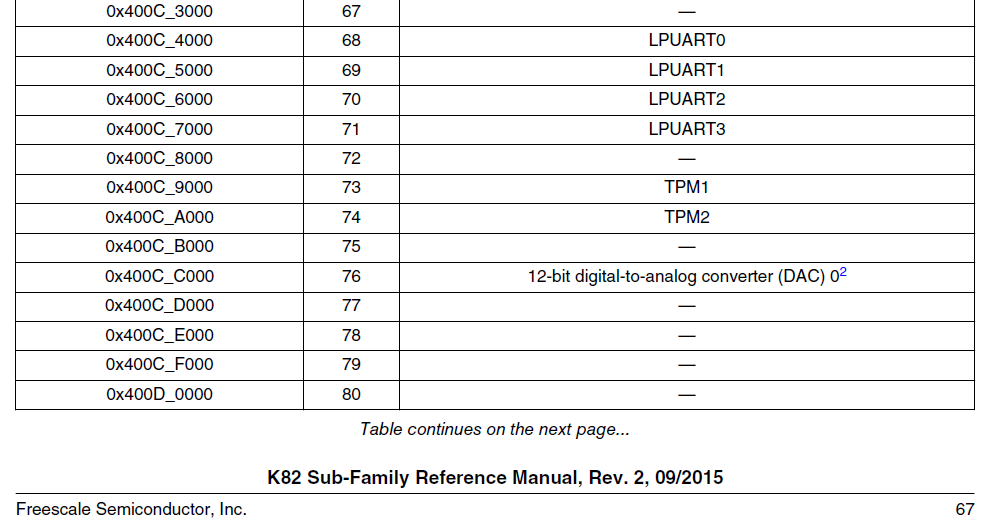

The LPUART0 module locates at slot 68 of AIPS1 as the Table 5-3. Peripheral bridge 1 slot assignments (continued) which I display as the screenshot.

You can write the AIPS1_PACR68 to set the access right for the LPUART0. You can set the AIPS1_MPRA to configure the different master access right.

Hope it can help you

BR

Xiangjun Rong