- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- Kinetisデザインスタジオ

- :

- Hardware reset on KDS 3.0.0

Hardware reset on KDS 3.0.0

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Hardware reset on KDS 3.0.0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi to all.

Is it possible to make a (real) hard reset to the CPU ?

There is the 'restart' button, but it doesn't make a Hardware reset to CPU.

Actually I'm using KDS 3.1.0 (but it is the same on 3.0.0), K64 microcontroller, Windows 10 64 bit

Can anyone help me ?

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Salvatore,

'restarts' sets the PC back to the reset vector and lets the code continue from there.

As you say, this is not the same as pulling the RESET line low. That thing is not supported with plain GDB as it is used in KDS, as this requires control over the Reset line through the debug (hardware) connection, and not every connection offers that. E.g. if you have 'only' SWD, the reset line might not be under control of the debug connection.

Additionally keep in mind that POWER-ON-RESET might be different from the normal RESET.

I hope this helps,

Erich

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Erich and thanks for the answer.

I wrote (incorrectly) 'power on reset' where I meant 'hw reset' (pulling low->high the reset line).

I'm using Multilink Universal and on 19pins connector (BDM ?) there is also a reset pin.

As previusly I said, with CW it works without problems (it manages the hw reset).

What I'd like is a 'procedure' or a command (possibly to associate to a 'button') to give the hw reset: do you think this is possible ?

The other way (extremely unconfortable) is make an external 'key' (on board or on emulator) and press it as needed (what actually I do.....)

Thanks in advance

Salvatore

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Salvatore,

I can confirm that it is possible to toggle the reset line with the Segger J-Link for download and restart, see Hardware Reset for ARM Cortex-M with Segger J-Link and Kinetis Design Studio | MCU on Eclipse

I have not tried the same with the P&E Multilink yet.

Erich

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Salvatore,

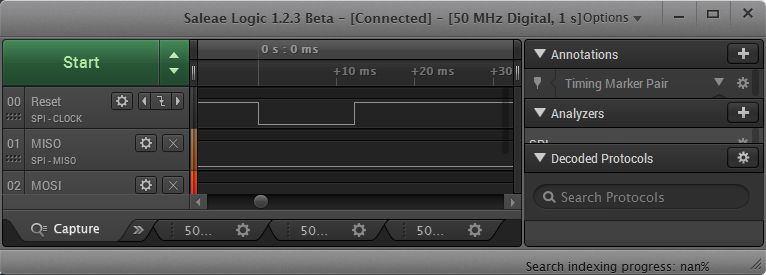

I quickly tried the same with KDS V3.x and the P&E Multilink Universal, and I can confirm it toggles the reset pin automatically (no need for a setting):

I hope this helps,

Erich

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Erich thanks for your response. I tried your suggestion and it works !!

Only a couple of informations:

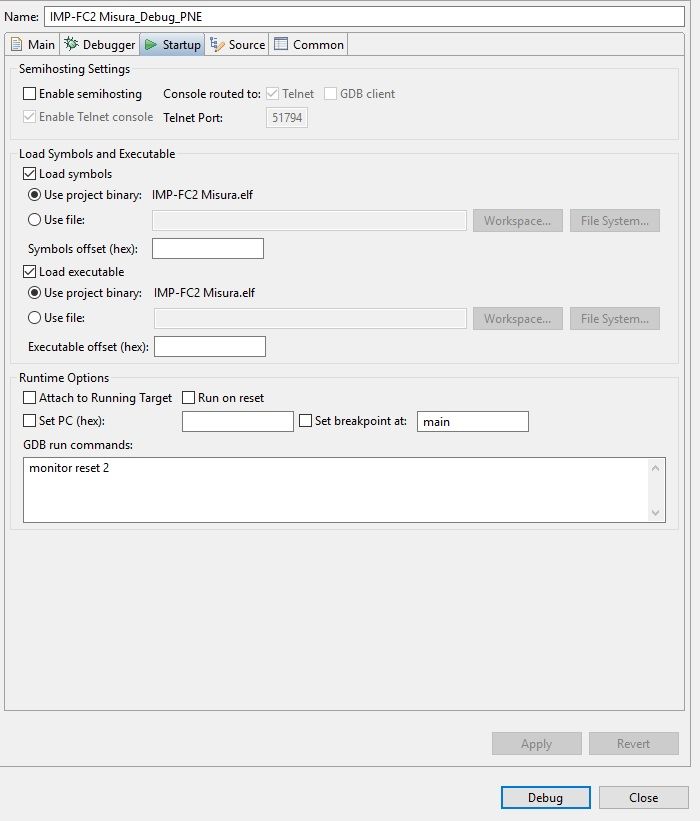

1) my KDS (3.1.0) / SDK (1.3.0) is for K64. It looks slightly different and you have to set the command "monitor reset 2" in a different position. Then here is no need to set the "2" on "type" box (also because it is not here ;-) ).

It looks like this:

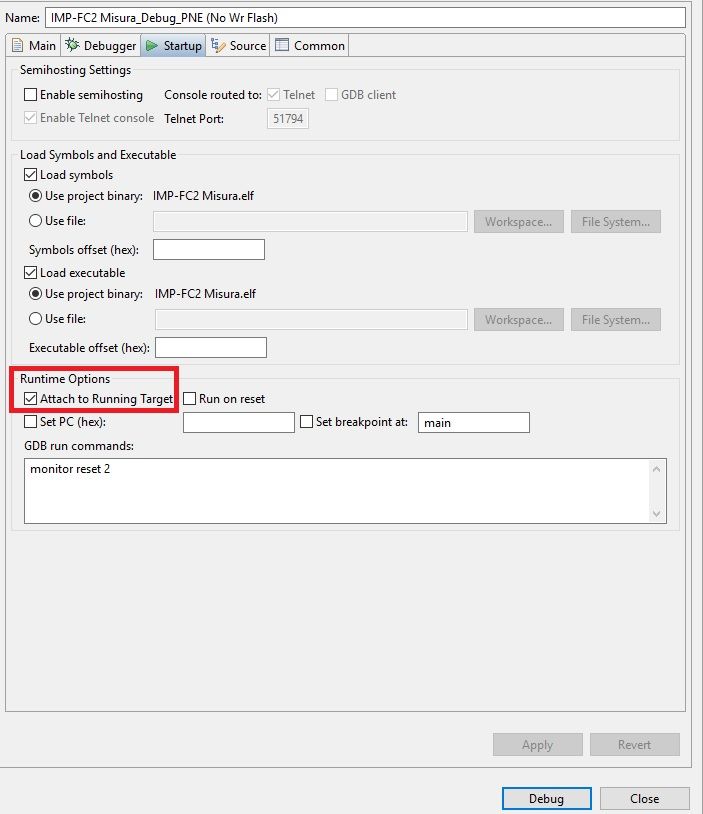

2) Into "attach" mode it doesn't work. But the funny thing is that the "restart button" doesn't work at all: it doesn't change the PC !!

Of course it doesn't work also without "monitor reset 2" command.

Here the "attach" setting (that doen't work !!!):

Thank a lot !!!

Salvatore

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Salvatore,

my screenshots are for Segger J-Link, yours are for P&E. They are different. And they behave differently as they have different GDB server implementations. I believe the P&E reset command does not support that additional argument (I think it is ignored).

Erich

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

OK Erich I understood the different screens from Segger & Multilink. I only posted the different screens to help other people using P&E Multilink ;-).

I confirm that it works also on my application giving an hardware reset.

What about the "attach problem" I mentioned ? Have you the same behavior (restart button does nothing) on Segger ?

I think this could be a KDS/GDB problem.

Salvatore

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This is how to generate a reset via software in an ARM. I realize it is not the same as pushing the physical reset button, perhaps this gets you closer to your goal.

reset_mcu.h: void __attribute__ ((noreturn)) reset_mcu( void );

reset_mcu.c:

/*

* The CPSID instruction is self-synchronized to the instruction

* stream and there is no requirement to insert memory barrier

* instructions after CPSID.

*/

static inline ATTR_NO_INSTRUMENT_FUNCTION void irq_disable( void )

{

__asm__ __volatile__ ("cpsid i");

}

/*

* Data Synchronization Barrier (DSB): Ensures that all explicit data

* memory transfer before the DSB are complete before any instruction

* after the DSB is executed.

*

* Ensure effects of an access to SCS take place before the next

* operation

*

* Ensure memory is updated before the next operation, for

* example, SVC, WFI, WFE.

*

* Vector table changes:

* If the program changes an entry in the vector table,

* and then enables the corresponding exception, a DSB

* instruction should be used between these two

* operations. This ensures that if the exception is

* taken after being enabled the processor uses the new

* exception vector. If the updated vector table is

* required immediately, for example if an SVC

* immediately follows an update to the SVC table entry

* via a store, then a DSB is also required.

*

* Memory Map modifications:

* If the system contains a memory map switching

* mechanism then use a DSB instruction after switching

* the memory map in the program. This ensures subsequent

* instruction execution uses the updated memory map, if

* the memory system makes the updated memory map visible

* to all subsequent memory accesses.

*

* Note:

* An ISB or an exception entry/return is required

* to ensure that the subsequent instructions are

* fetched using the new memory map.

*

* The memory barrier instructions, DMB and DSB, can be used to ensure

* that the write buffer on the processor has completed its operation

* before subsequent operations can be started. However, it does not

* check the status of the bus level write buffers. In such cases, if

* the system is based on AHB or AHB Lite, you might need to perform a

* dummy read through the bus bridge to ensure that the bus bridge has

* completed its operation.

*

* The Cortex-M0 processor (r0p0) and the Cortex-M0+ processor (r0p0)

* do not include a write buffer in their processor bus interface.

*

* Architecturally, a DSB instruction should be used after changing

* the VTOR if an exception is to be generated immediately and should

* use the latest vector table setting.

*

* In Cortex-M3, Cortex-M4 and Cortex-M0+ processors, accesses to the

* SCS have the DSB behavior, so there is no need to insert the DSB

* instruction.

*

* A DSB is required before generating self-reset to ensure all

* outstanding transfers are completed. The use of the CPSID I

* instruction is optional.

*/

static inline ATTR_NO_INSTRUMENT_FUNCTION void sync_barrier_data( void )

{

__asm__ __volatile__ ("dsb");

}

void __attribute__ ((noreturn)) reset_mcu( void )

{

/*

* A DSB is required before generating self-reset to ensure all

* outstanding transfers are completed. The use of the CPSID I

* instruction is optional.

* sync_barrier_data();

*/

irq_disable();

sync_barrier_data();

SCB_AIRCR = (SCB_AIRCR_VECTKEY(0x05FAU) | SCB_AIRCR_SYSRESETREQ_MASK);

for(;;)

{

;

}

}