- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: Connection closed by the GDB server.

Connection closed by the GDB server.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Connection closed by the GDB server.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using design studio, target is S32K146 , I was loading and running my project fine last night.

However when I tried to load and run again this morning, I keep getting the following:

Connection closed by the GDB server. and it fails to go through

This does not happen with other projects, I saw an earlier post recommending removing all the break points but that did not work for me.

What causes this to happen?

Thanks,

Koorosh Hajiani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Koorosh,

What debugger do you use?

Could you please specify what exactly was loaded the last time?

Thank you,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel

It is P&E open SDA using design studio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Koorosh,

I see that you posted it here as well:

From the console:

Does the project load something to DFlash?

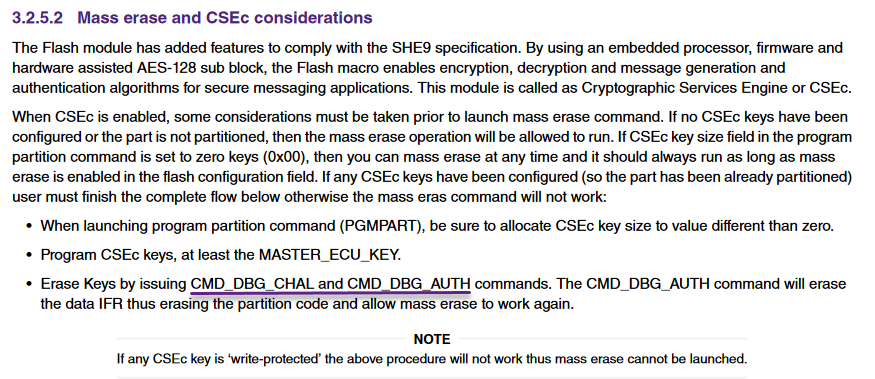

If so, the MCU has been already partitioned for EEPROM and CSEc (key space allocated), you would need to erase the partition with this commands:

AN12130 Production Flash Programming Best Practices for S32K1xxMCUs

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Daniel,

Thank you for your answer.

the part is patitioned and the Csec is enabled by the following: FTFC->FCCOB[2] = 0x03; /* FCCOB1 = 2b11, 20 keys */

However my question is howcome I can load and run other projects which are not enabling CSEC OR PARTITION THE PART.

Thanks,

Koorosh Hajiani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Koorosh,

To my understanding, when the programmer is loading this project, it tries to reprogram DFlash, whereas all the other project don't. Could you share the project? You can create a ticket if you don't want to share it here.

https://community.nxp.com/docs/DOC-329745

Thanks,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thanks for your response,

Here is what I don't understand , the same project that the CSEC is enabled ,by doing FTFC->FCCOB[2] = 0x03, I would change it to FTFC->FCCOB[2] = 0x00 or even at some point I commented out the whole portioning ,but still It would not work,

I can share the file and the linker file , by the way I'm using GREEN HILL compiler, the project itself is huge AND MY BOSS does not give me the per mission .

I'd send you the file where this is done + the linker file where I launched the command from:

by the way, how do I attach a file to this question.

Thanks,

Koorosh Hajiani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Koorosh,

It does not matter what the SW is doing once it has been programmed, but what is being loaded during the programming. That's what I understand from the console output.

Maybe S-record of the project would help.

There is this Use advanced editor option:

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using design studio for S32K .

I had a piece of code to partition the part (S32K146) , LAUNCHING THE COMMAND FROM RAM.

DID NOT ENABLE THE SECURITY, even when I comment the code out the problem persist.

I can load and run any other project without an issue . even my partition code was loading and running fine until the last morning.

here is the code to partition:

#if 0

uint8_t configure_part_CSEc(void)

{

uint8_t flash_error_status=0;

while((FTFC->FSTAT & FTFC_FSTAT_CCIF_MASK) != FTFC_FSTAT_CCIF_MASK); /* Wait until any ongoing flash operation is completed */

FTFC->FSTAT = (FTFC_FSTAT_FPVIOL_MASK | FTFC_FSTAT_ACCERR_MASK); /* Write 1 to clear error flags */

FTFC->FCCOB[3] = 0x80; /* FCCOB0 = 0x80, program partition command */

FTFC->FCCOB[2] = 0x03; /* FCCOB1 = 2b11, 20 keys */

FTFC->FCCOB[1] = 0x00; /* FCCOB2 = 0x00, SFE = 0, VERIFY_ONLY attribute functionality disable */

FTFC->FCCOB[0] = 0x00; /* FCCOB3 = 0x00, FlexRAM will be loaded with valid EEPROM data during reset sequence */

FTFC->FCCOB[7] = 0x02; /* FCCOB4 = 0x02, 4k EEPROM Data Set Size */

FTFC->FCCOB[6] = 0x04; /* FCCOB5 = 0x04, no data flash, 64k(all) EEPROM backup */

//FTFC->FSTAT = FTFC_FSTAT_CCIF_MASK; /* Start command execution by writing 1 to clear CCIF bit */

//while((FTFC->FSTAT & FTFC_FSTAT_CCIF_MASK) != FTFC_FSTAT_CCIF_MASK); /* Wait until ongoing flash operation is completed */

flash_error_status = FTFC->FSTAT; /* Read the flash status register for any Execution Error */

return flash_error_status;

}

//copied to RAM

void launch_flsh_com(void)

{

#if 1

#pragma asm

ldr r1, =0x40020000 ; <run_ocs_volt_once..C.3A.5CFramework_ZERV_v00.2E02.5CApplications.5CZERV_Framework.5CAppl.5Cobj.5CINF_CDD.>)

movs r0, #128 ; 0x80

strb r0, [r1, #0]

L1:

ldrb r0, [r1, #0]

lsls r0, r0, #24

bpl L1

; bx lr

#pragma endasm

#endif

#if 0

uint8_t configure_part_CSEc(void)

{

uint8_t flash_error_status=0;

while((FTFC->FSTAT & FTFC_FSTAT_CCIF_MASK) != FTFC_FSTAT_CCIF_MASK); /* Wait until any ongoing flash operation is completed */

FTFC->FSTAT = (FTFC_FSTAT_FPVIOL_MASK | FTFC_FSTAT_ACCERR_MASK); /* Write 1 to clear error flags */

FTFC->FCCOB[3] = 0x80; /* FCCOB0 = 0x80, program partition command */

FTFC->FCCOB[2] = 0x03; /* FCCOB1 = 2b11, 20 keys */

FTFC->FCCOB[1] = 0x00; /* FCCOB2 = 0x00, SFE = 0, VERIFY_ONLY attribute functionality disable */

FTFC->FCCOB[0] = 0x00; /* FCCOB3 = 0x00, FlexRAM will be loaded with valid EEPROM data during reset sequence */

FTFC->FCCOB[7] = 0x02; /* FCCOB4 = 0x02, 4k EEPROM Data Set Size */

FTFC->FCCOB[6] = 0x04; /* FCCOB5 = 0x04, no data flash, 64k(all) EEPROM backup */

//FTFC->FSTAT = FTFC_FSTAT_CCIF_MASK; /* Start command execution by writing 1 to clear CCIF bit */

//while((FTFC->FSTAT & FTFC_FSTAT_CCIF_MASK) != FTFC_FSTAT_CCIF_MASK); /* Wait until ongoing flash operation is completed */

flash_error_status = FTFC->FSTAT; /* Read the flash status register for any Execution Error */

return flash_error_status;

}

void launch_flsh_com(void)

{

#if 1

#pragma asm

ldr r1,=0x40020000

movs r0, #128 ; 0x80

strb r0, [r1, #0]

L1:

ldrb r0, [r1, #0]

lsls r0, r0, #24

bpl L1

; bx lr

#pragma endasm

#endif

// FTFC->FSTAT = FTFC_FSTAT_CCIF_MASK; /* Start command execution by writing 1 to clear CCIF bit */

// while((FTFC->FSTAT & FTFC_FSTAT_CCIF_MASK) != FTFC_FSTAT_CCIF_MASK); /* Wait until ongoing flash operation is completed */

}

Thanks,