- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- S9KEAZN64: How to disable the watchdog?

S9KEAZN64: How to disable the watchdog?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good morning.

My name is Daniele Fingolo and I am a software developer of SMH Technologies.

I'm trying to program the S9KEAZN64 device in question with a programmer that we developed.

We are able to communicate with the Arm Cortex interface via the SWD protocol.

So we are able to write to the core and device registers but we have a problem that seems to be attributable to the watchdog.

In fact we notice the following behavior:

When we power the microcontroller and bring the reset to a HIGH logic state, we periodically see that the reset goes LOW for a few moments and then returns high. This behavior is repeated by resetting the device. Therefore it would not be possible to continue programming if the device is reset after a certain time interval (about twentythree microseconds).

But we have seen that by putting the core in HALT, this behavior no longer occurs.

So we speculated that it depends on the watchdog.

But with the code that we have developed we cannot disable it, because once the core with the code to disable the watchdog is restarted, the latter is not disabled.

I tried to put the same code both in RAM and Flash. In both the cases the watchdog hasn't been stopped.

Attached you will find the source code .C we used and it doesn't seem to work.

The watchdog refresh is not working either.

Attached are also the acquired images of the reset signal.

Can you help me?

I need a specific procedure to disable the watchdog for all the duration of the programming process.

Thank you in advance.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

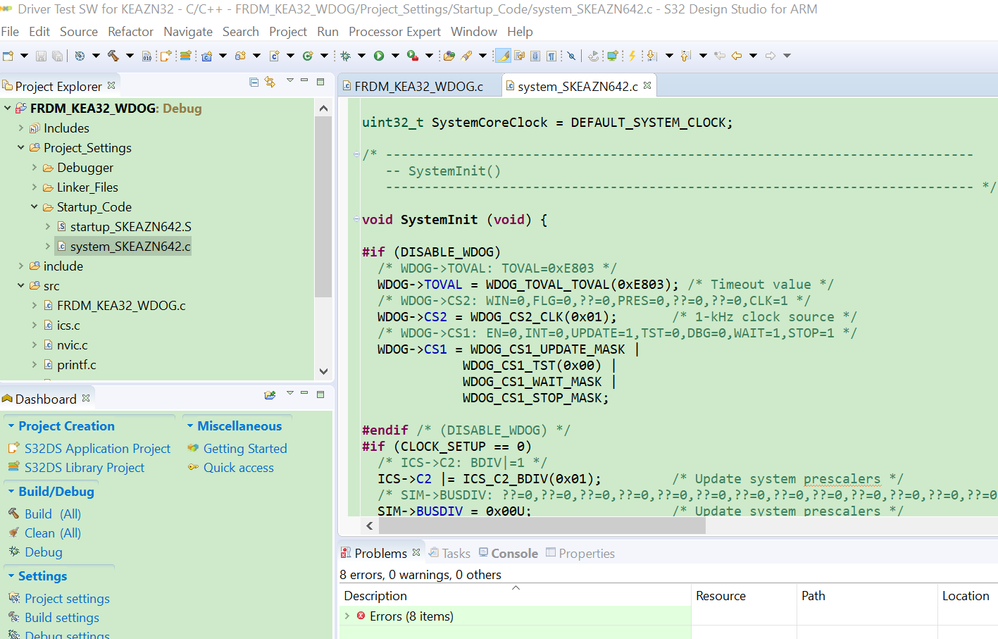

It is the S32DS project, not the MCUXPresso IDE project. S32DS IDE can be downloaded from this link:

S32 Design Studio IDE for Arm® based MCUs | NXP

BTW, Do you use the new KEA chip which didn't download the code previously?

If yes, the RESET pin goes low periodically is correct to the new chip.

After you download the code, which disable the Watchdog, then your reset pin will be high.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry and Mark,

I resolved the problem. Thank you both. I really appreciated.

I tried to compiled the example "FRDM_KEA64_WDOG" you cited and it works.

The problem is that with MCU Xpresso seems not possible to built a working image even if you chose the correct cortex Architecture. In fact I tried with simple "while(1)" code and I see always the effect of reset pin (periodically goes LOW after about 25 microseconds).

After I compiled with S32DS IDE and the image works both in FLASH memory and in RAM memory.

The effect we saw on Reset pin in properly due to an uncorrect image inside the memory. In fact if i don't write nothing in the memory or if I write the FLASH with a simple image built with MCUXpresso, then I see the RESET pin goes low periodically. (25 microseconds)

Instead If I write a sample image built with S32DS IDE, I don't see the RESET pin goes low, expect if i don't disable the watchodog (that goes LOW after some milliseconds and not after about 25 microseconds in the case of the problem in question).

I started originarly by writing and executing the image directly in the RAM. In this case if the watchdog is not diable or fed then the Reset is executed and the process tries to start to read the flash memory. If nothing is written in the flash, the Reset pins goes low periodically. (the effect in question).

So in conclusion, I think that is necessary to use S32DS IDE to build image for KEA family , even if for other Kinetis devices works also the MCUXpresso.

Thank you again

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks so much for your more details.

To the KEA, it is the auto chip, so mainly supported by the S32DS or the old KDS, or CW.

The new MCUXPresso IDE just support the KE series, I didn't find the KEA series.

So, You are right, you can use the s32DS IDE, you also can find the KEA driver code is based on the S32DS IDE.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniele Fingolo,

You need to disable the watchdog after you enter the systemInit, after reset, this code will be executed to disable the watchdog.

You can refer to the attached S32DS code.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Thank you for the suggestions. I appreciated it.

I compiled your source files using MCU Xpresso. I used the same linker directives as you. I wrote it in the FLASH.

The result is the same. I see that the RESET pin goes low periodically.

I tried another firmware that I haven't source files, and it hasn't the issue.

So I think that there is some set up to do at the begin of the code that no regards the watchdog.

I mean, I need also the disabling of watchdog, but this problem regards another thing.

I think that @MarkButcher has reason.

And I think that it concerns KEA devices, and not other families of Kinetis.

Do you have a sample software specific for the device in question?

I suppose that can resolve the problem.

Thank you in advance.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is the S32DS project, not the MCUXPresso IDE project. S32DS IDE can be downloaded from this link:

S32 Design Studio IDE for Arm® based MCUs | NXP

BTW, Do you use the new KEA chip which didn't download the code previously?

If yes, the RESET pin goes low periodically is correct to the new chip.

After you download the code, which disable the Watchdog, then your reset pin will be high.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Daniele

I have reference binaries here for the device in question which you may be able to use:

https://www.utasker.com/kinetis/FRDM-KEAZ64Q64.html

Depending on an input (see text at the link) it will either disable the watchdog or configure it and service it when operating).

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniele

The watchdog disable code is correct so I doubt that the code is being executed.

The reset waveform is typical of a processor that has no code loaded to its flash memory - it immediately crashes and the reset sequence repeats forever every approx. 25us. Do you have correct start-up code to call your main?

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

Thanks for the suggestion it was enlightening.

I tried to load a firmware already compiled by our client into FLASH and the periodic RESET does not occur.

So I tried to write the firmware that I shared with you in FLASH and the periodic phenomenon on the RESET pin still occurs. The same happens if I load it into RAM using the ARM debug interface.

So I deduce that the problem concerns something that needs to be done at the beginning of the firmware which I have no idea of.

It seems that it is necessary to implement a certain procedure to prevent the device from entering a periodic reset state.

Do you have sample software with the initial settings for this device?

We have programming experience of several Kinetis families, and in the others at the beginning of the firmware execution in RAM, we deactivate the watchdog without problem and without inserting other rotuines. In fact, I tried with the firmware made for other Kinetis and we have the same periodic signal on the RESET pin.

So I think it's a matter of these KEA family..

Thank you in advance.

Regards