- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Clock idle level on SPI port LPC54628 not correct during DMA?

Clock idle level on SPI port LPC54628 not correct during DMA?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Clock idle level on SPI port LPC54628 not correct during DMA?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

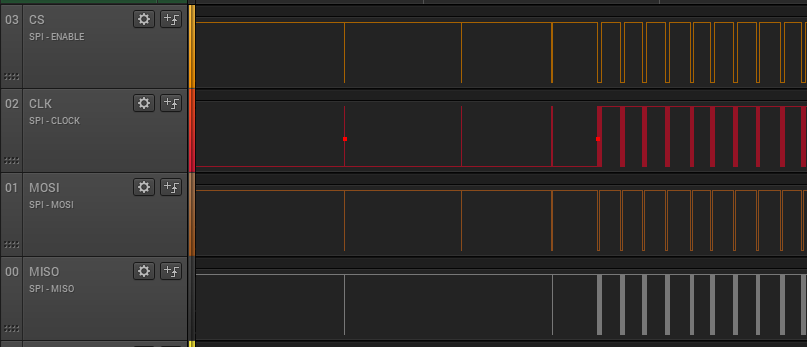

we have a design with a LPC54628. Flexcomm6 is configured for SPI Master and is basically working fine (using DMA transfers). However, when looking at CPOL/CPHA, there is something not quite right. During "normal" SPI read/write (setup of slave device etc) the clock idles low between transfers as it should, but once I start DMA, the clock line idles high. No matter if CPOL bit is set or not, the idle level of the SCLK signal is always high between DMA transfers. I have verified the contents of the CFG register and this is 0x05 (as expected) which is CPHA=0 and CPOL=0. Regardless of this, the clock line idles high between DMA transfers.

Whats going on ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Carsten,

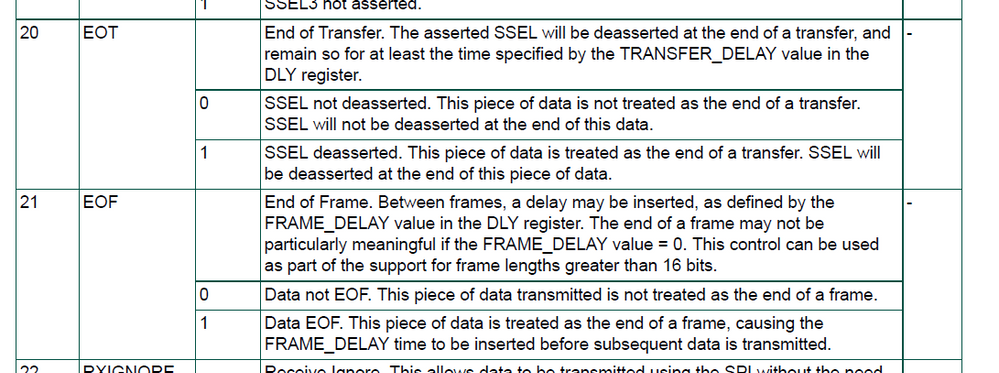

I suppose that you clear the EOT bit in the FIFOWR register when you write the data to FIFO. For detailed information, pls refer to Table 465. FIFO write data register (FIFOWR - offset 0xE20) bit description in UM10912.pdf.

Especially section 26.6.14 FIFO write data register.

I suggest you try to set both EOT and EOF bits and set the TRANSFER_ DELAY in SPI Delay register as non-zero value, then try to see the CLK logic.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

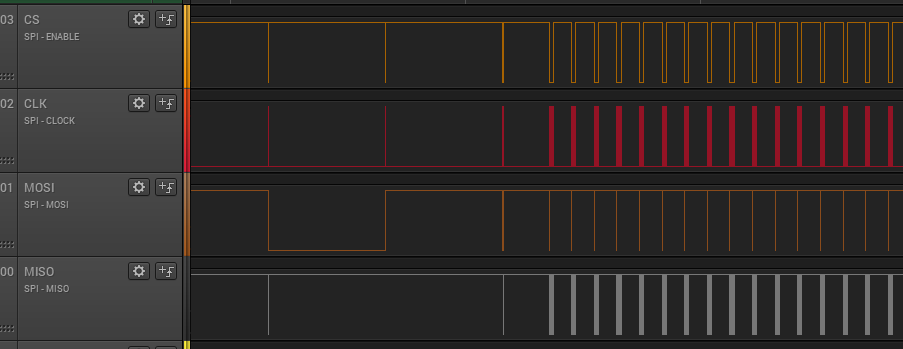

thanks for feedback, some success, but not quite there.....

I tried setting:

masterXfer.configFlags = kSPI_FrameDelay | kSPI_FrameAssert;

when I start the DMA transfers, and:

SPI6->DLY=0x1111;

when initializing the SPI port. This seemed to work for a while, however, at some point I no longer get called back by the "DMA done", this happens after approx 4000 to 50000 DMA transfers ! Any idea whats wrong ?

Final code that I'm testing:

void initSPI6() {

spi_master_config_t masterConfig = {0};

CLOCK_AttachClk(kFRO_HF_to_FLEXCOMM6); // Flexcomm6 uses FRO (48 MHz which is max for Flexcomm)

// reset FLEXCOMM for SPI

RESET_PeripheralReset(kFC6_RST_SHIFT_RSTn);

SPI_MasterGetDefaultConfig(&masterConfig);

masterConfig.polarity = kSPI_ClockPolarityActiveHigh; // CPOL=0

masterConfig.phase = kSPI_ClockPhaseFirstEdge; // CPHA=0

masterConfig.baudRate_Bps = 10000000; // 10 MHz clock (9.615 MHz)

SPI_MasterInit(SPI6, &masterConfig, CLOCK_GetFlexCommClkFreq(6));

SPI_SetDummyData(SPI6, 0xFF);

// See: https://community.nxp.com/message/1336345?commentID=1336345#comment-1336345

// Code below is the same as: SPI6->DLY=0x1111;

spi_delay_config_t dly_config;

dly_config.frameDelay=1;

dly_config.transferDelay=1;

dly_config.preDelay=1;

dly_config.postDelay=1;

SPI_SetTransferDelay(SPI6, &dly_config);

}

masterXfer.txData = dmaTXBuff; // Command in first byte!

masterXfer.rxData = (unsigned char*)&(dataFIFO[0][0]); // (first) Buffer for data received

masterXfer.dataSize = sizeof(dataFIFO[0]); // Number of bytes, each FIFO word is 7 bytes in size PLUS the one byte answer to the "read FIFO command"

// See https://community.nxp.com/message/1336345?commentID=1336345#comment-1336345

masterXfer.configFlags = kSPI_FrameDelay | kSPI_FrameAssert;

SPI_MasterTransferDMA(SPI6, &masterHandle, &masterXfer);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Carsten,

The DMA issue is another question, I think you can refer to the DMA register in debugger to get the cause.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Another issue or not, I'm not sure :smileywink:

It happens only when the EOT/EOF and DLY are used. The callback (IRQ) that should happen when the DMA finishes, is not coming. As I wrote, this can happen after 4000 DMA transfers or after 50000 transfers. If the EOF/EOT/DLY is not used, the DMA can run for millions and millions of transfers.

How these two things are related I don't (yet) know....

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Garsten,

If setting the EOT/EOF bits can leads to DMA issue, so pls clear the bits as you had done. I do not think the high level of SCLK between two Bytes has any disadvantage if the data transferred is okay.

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is also how we run the code in our tests now. But, it is a little worrying why the DMA stops with these 2 bits set, do you perhaps have time to do a test in your end ?