- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC55S69 : nIRQ pin allocation

LPC55S69 : nIRQ pin allocation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC55S69 : nIRQ pin allocation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi !

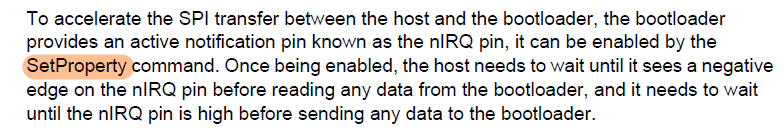

on page of UM 207-209 I can read this kind of recommendations:

"

The bootloader also supports the active notification pin (nIRQ pin) to notify the host

processor it is busy or ready for new commands/data. See below figure for the typical

physical connection between the host and the bootloader device.

....

To accelerate the SPI transfer between the host and the bootloader, the bootloader

provides an active notification pin known as the nIRQ pin, it can be enabled by the

SetProperty command. Once being enabled, the host needs to wait until it sees a negative

edge on the nIRQ pin before reading any data from the bootloader, and it needs to wait

until the nIRQ pin is high before sending any data to the bootloader.

"

But it is not clear what exact GPIO pin can be used for those purposes. And Exact format of message for configure it.

Do you have more info about it ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene,

As you mention, in the reference manual doesn't explain which pin is the nIRQ, in previous LPC the same ISP pin was used as nIRQ. So maybe is the same with this. I will test this to confirm this information

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alexis !

Could it be possible to also give recoomendation about SPI transfer speed and data packet what is optimal for ISP flashing.

Flash memory have limited write/erase timimg and dosn't have sense to deliver data faster.

So if no any nIRQ pin what is normal speed of flashing can be visible ?

From other side , flashing should be as fast as possible for save time in production.

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene,

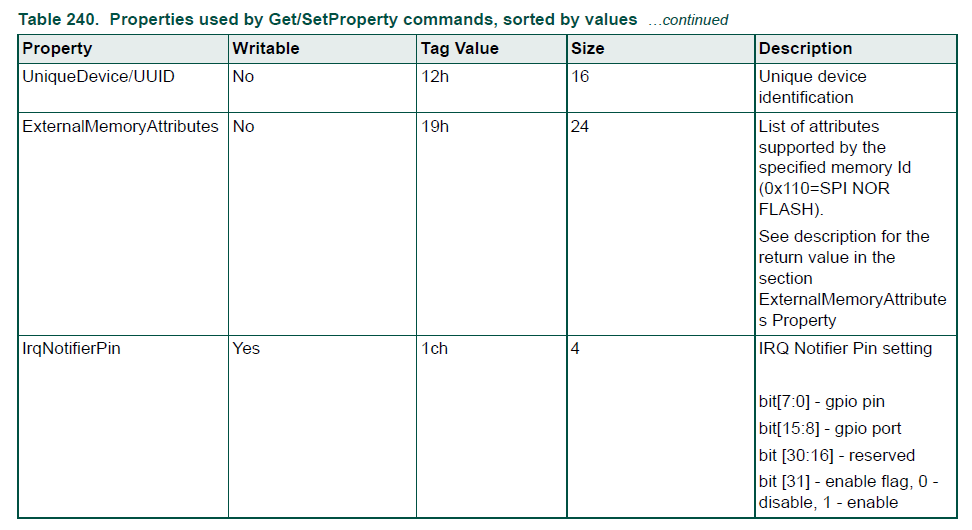

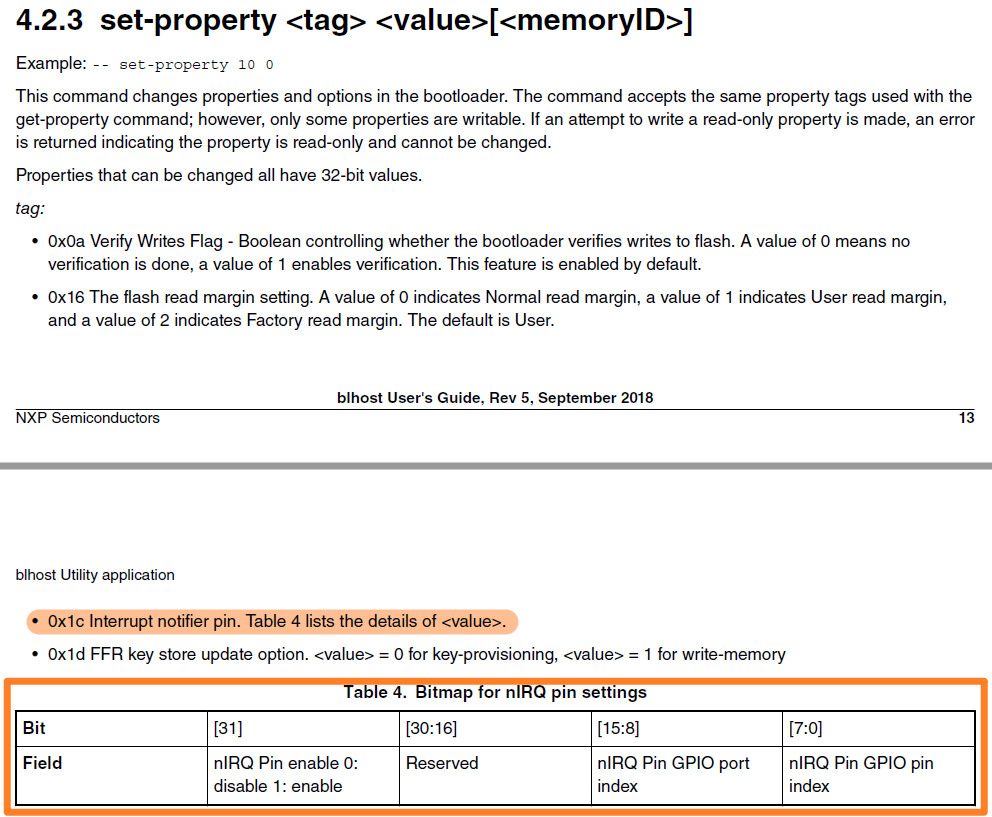

I found how it works this pin.

The nIRQ pin is configurable. It can be configured by blhost command as shown below.

The details can be found in UM and blhost User's Guide.pdf (located at SDK/middleware/mcu-boot/doc).

Also, the configuration need it for the SPI should be CPOL = 1, CPHA = 1 and the baudrate should not be higher than 2000 kbit/s.

I hope this helps you.

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alexis !

So basically any GPIO pin ( from port 0 or 1) can play this role ?

Can be reuse ISP pin ? In this case it should be reinitialized by bootloader from input to output and may be it is locked by bootloader

as input only.

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene,

This should not affect the bootloader since after a reset the bootloader will return to its original state so the pin will be available after a reset.

Best Regards,

Alexis Andalon