- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC66S69 : Secure GPIO output

LPC66S69 : Secure GPIO output

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC66S69 : Secure GPIO output

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello !

Do I understand right and when GPIO pin from Bank 0 is marked as secure, it is not only not possible to read it state from NonSecure world but also is not possible to set output state ?

in UM it is not so clear about output behaviour.

Idea is to close control access to some GPIO pins what configured as output.

Is this possible ?

By the way what peripheral block of LPC can be use in similar ways like AIPS in K82 ?

I have RTOS tasks what running in nonsecure world with User privileges and I would like to limit set of peripherals

what can be accessed with User privileges . For K82 it was easy to done by using dynamic tables what update AIPSx gates at the same time as MPU tables.

But how in this MCU I can limit access of User task to one FLEXCOMM interface only ?

When task context is in -> eanble access with User privileges , when out - disable.

Is this possible ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Eugene Hiihtaja,

1) "Do I understand right and when GPIO pin from Bank 0 is marked as secure, it is not only not possible to read it state from NonSecure world but also is not possible to set output state ?"

-> If the GPIO config as secure state, yes, only CPU-S can read it. The CPU-S can config it, CUP-NS can't.

About the secure GPIO, the main function is when one pin is configured as peripheral pin, for example UART pin,

and the config the UART in secure state, then the avoid CPU-NS read the GPIO state, only CPU-S can access it.

About the detail introduction of Secure GPIO, you can have a look at this application note:

https://www.nxp.com/docs/en/application-note/AN12326.pdf

2) About the freeRTOS question, you can take a new ticket in this thread:

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello !

I need to separate pins from group 0 to secure and nonsecure accesible.

I undestand if individuals pins marked as secure they can be read/write via SGPIO only.

Remains one will be accessed from NonSecure world as usually.

Is this right way to split GPIO0 pins for Secure and Nonsecure groups ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Eugene Hiihtaja,

From your description , I think your requirement is not SGPIO function,

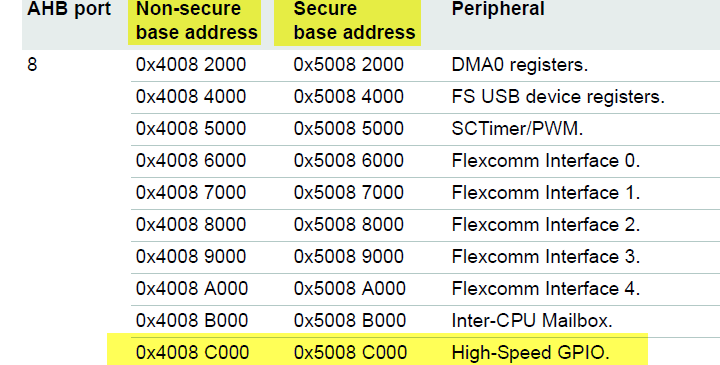

it should be TrustZone . The implementation of ARM TrustZone for CPU0 involves using address bit 28 to divide the address space into potential secure and non-secure regions.

In Table 5 of UM, provides details of the addresses for APB peripherals. APB peripherals have both secure and non-secure access possibilities.

So we can only set the whole GPIO to secure space or Non-secure, can't split GPIO0 pins for Secure and Nonsecure groups.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

But I can see separate peripheral called HS Secure GPIO. I assume some individual pins start to belong to Secure GPIO and controlled from secure world and remains one can be controlled via NonSecure world by using GPIO peripherals.

And TZ configuration will be done accordingly.

Also GPIO releated to peripherals will be added to Secure domain for avoid any read from NonSecure side.

Or how it works ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Eugene,

OK, I know your meaning.

Yes, you can set some of the GPIO as secure GPIO, some as normal GPIO.

About how to config them as secure GPIO, please refer to the AN12326 I mentioned before.

And also there is Secure GPIO demo under SDK, this demo just config one pin as Secure GPIO.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------