- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- SPI Slave Configuration for the LPC1549 ( LPC15xx )

SPI Slave Configuration for the LPC1549 ( LPC15xx )

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI Slave Configuration for the LPC1549 ( LPC15xx )

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm currently evaluating the SPI slave functionality of the LPC1549.

I'm wondering if there is any examples not using the ROM API, I'd like to be able to tweak the ISR to my liking and have more control on what's being transmitted.

Is there a data rate limit?

It seems like a feature that even the user guide lacks proper explanation and configuration of this state for the peripheral.

Currently I have the following configurations using LPCOPEN :

for this example I'm using SPI0

- Set GPIO direction for general SPI and a CS

- Set the SWM settings corresponding to the proper PINASSIGN banks for SWM_SPI0_MOSI_IO, SWM_SPI0_SCK_IO, and SWM_SPI0_MISO_IO

- I then set the CS the same as if I were to be in Master mode ( Except CS is set to input ).

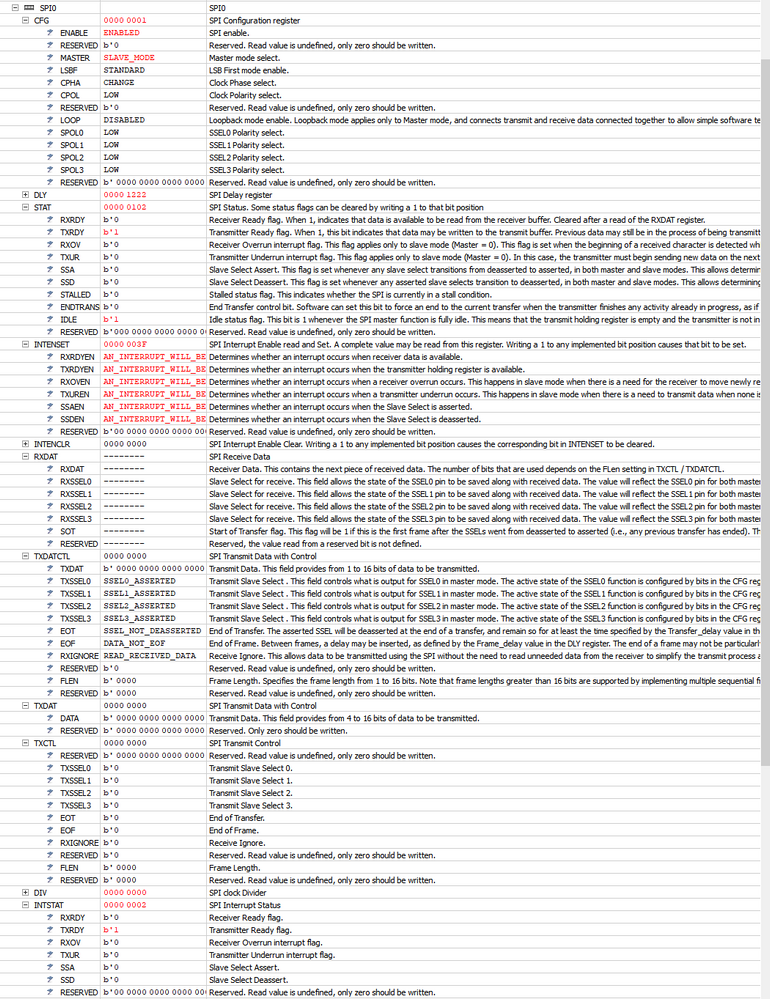

After initialization , the following configurations are set in the SPI0 peripheral register :

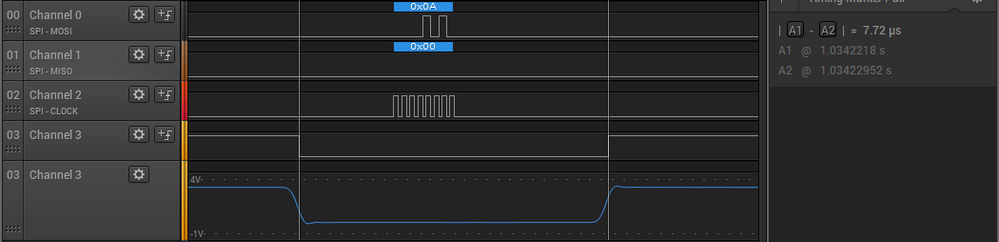

Once I send the following capture, The SSA ( Slave Select Assert ) and SSD ( Deassert ) are found to be set, but I would expect the RXRDY to be set as well.

Let me know if you guys require additional information, I'd love to chat about this!

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor Maslov,

It seems there isn't SPI slave demo about LPC1549 under LPCopen.

Could you please show your code ?

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This morning, I've decide to try the ROM polling example.

I'm currently using the ROM example as provided, using 8 bit instead of 16 bit transfer, and only 1 byte for my receive side.

I'm sending the same byte from the snippet above.

Here are the two lines I've modified to work with the 8 bit 1 byte "message"

I'd like to reinstate that I find it odd the lack of documentation on slave mode for the LPC15xx devices. Is there any documentation with additional descriptions on it's functionality & configuration?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor ,

Sorry there isn't any other documents, only User Manual and the demo.

You can combine the Demo with "Chapter 39: LPC15xx SPI API ROM driver routines"

and "25.6 Register description" to config.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------