- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- PF3000 VLDO34in level issue

PF3000 VLDO34in level issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Support,

We have ever received a review update (see below information) that asks us not to follow the imx7D saber design but change to 3.6V input for VLDO34in pin.

Now, we use a fix 3.6V LDO for it to dropout the voltage from VBAT to 3.6V but now we see the that the DC range test result is 3.582~3.624V, Vrms test result is 3.59~3.6V. The datasheet shows the range is 2.8~3.6V. I see the explain from your support team shows there is only linkage current issue. Will my test result have any chip damage issue on this pin?

====

Keep PMIC_PWR(=3.75V) clean, always no pulse or spike than 4.5V for VLDO34IN (pin #21), this DC 3.75V voltage is OK. Suggest to add one more 4.7uF cap for VLDO34IN noise or pulse decoupling. The reason is as below:

PF3000 datasheet was updated with VLDO34VIN pin max rating from 4.5V to 3.6V in Datasheet Rev7.0. The 7D reference design was not updated.

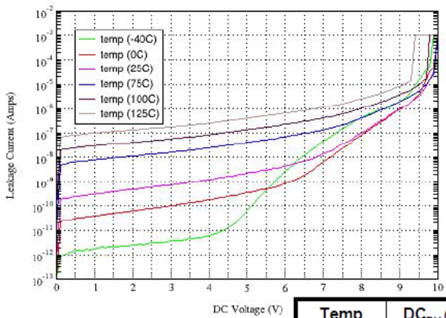

The VLDO34IN can only accept 3.6V input is due to the pin is using a 3.6V ESD structure. With supply a little bit higher than 3.6V would not definitely damage the pin but take the pin into possibility of leakage. And the leakage will increase with the voltage goes higher, its level is very small. See below, it is good if you have chance to reduce main power supply to exactly 3.6V.

====

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Franky,

According to the datasheet, exceeding the 3.6V on VLDO34IN ratings may cause malfunction or permanent damage to the device, however, for the particular case of this VLDO34IN regulator, this limit is documented because beyond 3.6V, the ESD protection can be sensitive to voltage transients. So, exceeding the 3.6V with, in your case, 3.624V, I don’t think it could cause permanent damage to the device.

Although it is important to mention that NXP does not recommend to exceed the rating, but it is decision of the customer it the risk is acceptable.

Have a great day,

Jose

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Franky,

According to the datasheet, exceeding the 3.6V on VLDO34IN ratings may cause malfunction or permanent damage to the device, however, for the particular case of this VLDO34IN regulator, this limit is documented because beyond 3.6V, the ESD protection can be sensitive to voltage transients. So, exceeding the 3.6V with, in your case, 3.624V, I don’t think it could cause permanent damage to the device.

Although it is important to mention that NXP does not recommend to exceed the rating, but it is decision of the customer it the risk is acceptable.

Have a great day,

Jose

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Any reply for this question?