- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- High speed SCI

High speed SCI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using a S12ZVCA with the 12MHz external crystal. I need to have a 250 kbps baud rate on SCI.

I have try to receive 4 bytes, but only receive the 1st bytes.

Processor Expert setting as follow:

void main(void){

............

i=0;

while(i<bLen) {

RxFlag = AS1_RecvChar(&ReceiveChar);

if(RxFlag != ERR_RXEMPTY)

bBuf[i++] = ReceiveChar;

}

............

}

byte AS1_RecvChar(AS1_TComData *Chr){

byte Result = ERR_OK; /* Return error code */

byte StatReg = SCI1SR1; /* Read status register */if (StatReg & SCI1SR1_IDLE_MASK) {

(void) SCI1DRL; /* Dummy read of the SCI1DRL to clear the flag*/

SerFlag |= IDLE_ERR;

}

if (StatReg & (SCI1SR1_OR_MASK|SCI1SR1_NF_MASK|SCI1SR1_FE_MASK|SCI1SR1_PF_MASK)) { /* Is any error flag set? */

Result = ERR_COMMON; /* If yes then set common error value */

} else if ((StatReg & SCI1SR1_RDRF_MASK) == 0U) { /* Is the reciver empty and no error is set? */

return ERR_RXEMPTY; /* If yes then error */

} else {

/* Else branch due to MISRA compliance */

}

*Chr = SCI1DRL; /* Read data from the receiver */

return Result; /* Return error code */

}

Do you have any recommend?

Best Regards,

Aaron

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

If the value of the SCI1SR1 register is 232 it means the overrun occurred.

When Rx buffer is not empty (not read) and further data are received the overrun flag is set. That’s why the data are lost.

See chapter "14.3.2.7 SCI Status Register 1 (SCISR1)":

Overrun Flag — OR is set when software fails to read the SCI data register before the receive shift register receives the

next frame. The OR bit is set immediately after the stop bit has been completely received for the second frame. The data in the shift register is lost, but the data already in the SCI data registers are not affected. Clear OR by reading SCI status register 1 (SCISR1) with OR set and then reading SCI data register low (SCIDRL).

Your bus clock frequency is 6.25 MHz. So, increase the bus clock frequency to maximum - 32MHz can help.

Let me know if it helped you.

Best regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

My project as attachment.

SCI baud rate is 250,000bps

The error as following:

if (StatReg & (SCI1SR1_OR_MASK|SCI1SR1_NF_MASK|SCI1SR1_FE_MASK|SCI1SR1_PF_MASK)) { /* Is any error flag set? */

Result = ERR_COMMON; /* If yes then set common error value */

StatReg = 232 when receive the CH2(blue). Sometime read 2 bytes

Yellow: Send command from S12ZVCA_SCI_TX to bq76PL455A_RX (Data: 0x.......81 00 51 00 15 AC)

Blue: Feedback from bq76PL455A to S12ZVCA (Data: 0x00 80 01 A0)

I have been try using PC to instead of bq76PL455A. The S12ZVCA can transmit command to PC and receive PC feedback. The different is PC take a longer time (>1s)

from S12ZVCA transmitted command(Yellow) to starting receive feedback(Blue).

Do you have any recommend?

Best Regards,

Aaron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

If the value of the SCI1SR1 register is 232 it means the overrun occurred.

When Rx buffer is not empty (not read) and further data are received the overrun flag is set. That’s why the data are lost.

See chapter "14.3.2.7 SCI Status Register 1 (SCISR1)":

Overrun Flag — OR is set when software fails to read the SCI data register before the receive shift register receives the

next frame. The OR bit is set immediately after the stop bit has been completely received for the second frame. The data in the shift register is lost, but the data already in the SCI data registers are not affected. Clear OR by reading SCI status register 1 (SCISR1) with OR set and then reading SCI data register low (SCIDRL).

Your bus clock frequency is 6.25 MHz. So, increase the bus clock frequency to maximum - 32MHz can help.

Let me know if it helped you.

Best regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

The overrun issue is resolved by 32MHz bus clock. Thank you.

But the next issue is program dead-loop in ISR(AS1_Interrupt).

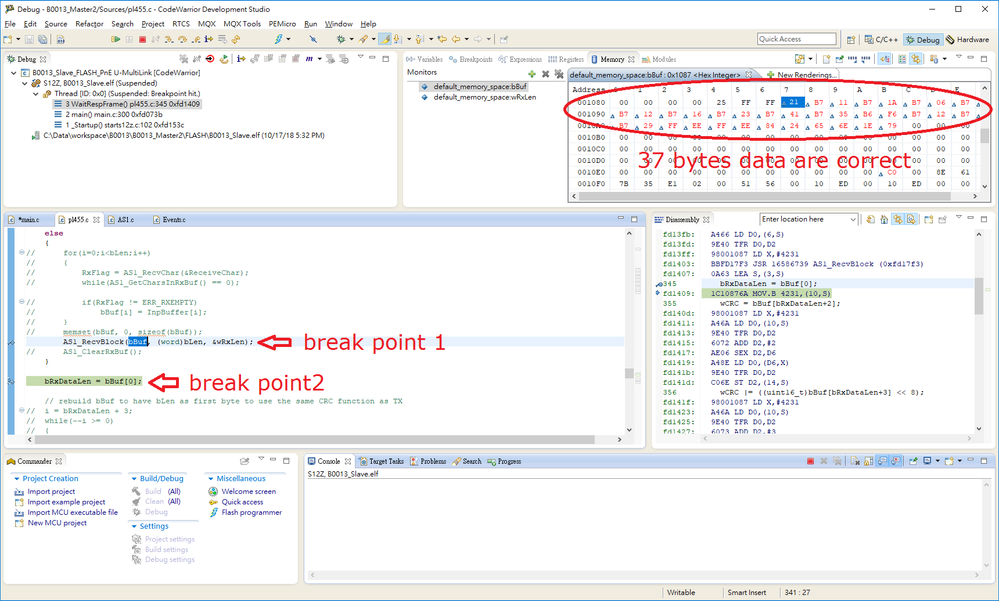

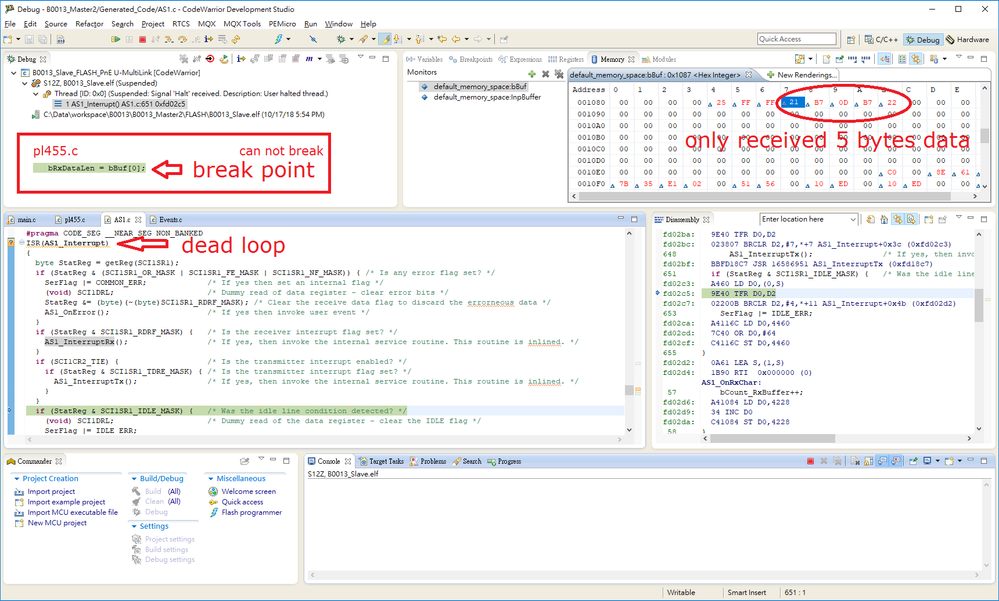

We use DEBUG step by step. And we can see dead-loop at "main.c line 300"

main.c

line 300: nSent = WaitRespFrame(bFrame, 37, 503); // Call pl455.c

Press suspend for check the SCI1 registers

We setting BREAKPOINT to "pl455.c line 341 & 345". Then run it. bBuf can received 37 bytes data.

pl455.c

line 341: AS1_RecvBlock(bBuf, (word)bLen. &wRxLen); // Break Point

line 345: bRxDataLen = bBuf[0]; // Break Point

We setting BREAKPOINT to "pl455.c line 345". Then run it. Program can not stop at BREAKPOINT.

pl455.c

line 345: bRxDataLen = bBuf[0]; // Break Point (Can not stop)

How to stop ISR(AS1_Interrupt) and return back?

Please see attachment.

Best Regards,

Aaron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

We are adding the mark of code. It can resolve my issue.

Why the idle interrupt request(SCI) trigger frequently?

What situation were trigger this ilde IRQ ?

Best Regards,

Aaron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

I'm glad you solved your issue.

IDLE interrupt indicates that receiver input has become idle.

You can refer to "14.5.3.1.5 IDLE Description" and "14.3.2.7 SCI Status Register 1 (SCISR1)" in the reference manual.

"The IDLE interrupt is set when 10 consecutive logic 1s (if M = 0) or 11 consecutive logic 1s (if M = 1)

appear on the receiver input. Once the IDLE is cleared, a valid frame must again set the RDRF flag before

an idle condition can set the IDLE flag. Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE

set and then reading SCI data register low (SCIDRL)."

I hope it helps you.

Best regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

What does 1s and M mean?

The MCU is in high loading during SCI IDLE for a long time.

Set IDLE ==> Clear IDLE ==> Set IDLE ==> Clear IDLE ==> .............

Is it necessary to handle interrupt of IDLE in SCI communication?

When does the interrupt of IDLE must be handle in SCI?

Best Regard,

Aaron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

The M bit is in the SCIDR1 register:

Data Format Mode Bit — MODE determines whether data characters are eight or nine bits long.

Logic 1s means logic 1.

That is why if M=0 => ten consecutive logic 1 and if M=1 => eleven consecutive logic 1

Enable the transmitter, interrupts, receive, and wake up as required. So, it is not necessary to enable the idle interrupt.

For example, if you have no space(gaps) between data send characters you can generate delay between them using the idle character. Clearing and then setting the TE bit during transmission queues an idle character to be sent after the frame currently being transmitted.

I hope it helps you.

Best regards,

Diana