- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K 40 BITS TRANSFER SPI DMA

S32K 40 BITS TRANSFER SPI DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K 40 BITS TRANSFER SPI DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

My target is S32K and I'm trying to talk to a slave device on SPI.

The slave requirement calls for 40 bits transfer during which the Chip Select needs to be asserted.

Processor Export Does not seem to work for 40 bits (5 bytes)/frame. I got it to work for 32bits and I believe any multiple of 4 bits/frame. If this is true , is there a workaround available?

I even tried to configure the SPI for 8bits/frame and control the chip_select as a GPIO outside the PE code but I couldn't get it to work completely.

the project is attached.it is a modified version of an example project.

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

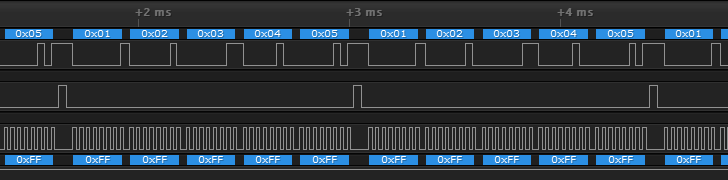

I modified the LPSPI_s32k144 example code (only the main loop) and it seems it works with a continuous transfer, 8-bit frame.

for(;;){

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

LPSPI1->TCR = 0x7B280007;

/* CONT=1: Continuous transfer enabled */

/* CONTC=0: Command word for start of new transfer */

/* RXMSK=1: Mask received data*/

/* FRAMESZ=7: # bits in frame = 7+1=8 */

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

LPSPI1->TDR = 0x1; /* Transmit data */

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

LPSPI1->TDR = 0x2; /* Transmit data */

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

LPSPI1->TDR = 0x3; /* Transmit data */

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

LPSPI1->TDR = 0x4; /* Transmit data */

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

LPSPI1->TDR = 0x5; /* Transmit data */

}Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thanks for your response,

I believe it is my fault that I was not clear in my question. I HAVE IMPEMENTED THIS LONG TIME AGO NOT USING DMA.

I was referring to the LPSPI DMA example project which uses the processor export configuration. It works with 32bits/frame , 8bits/frame

however my slave device requires 40 bits/frame and the SPI DMA does not seems to like it.

for throughput purposes I NEED TO THIS USING DMA.

THANKS FOR YOUR EFFORT but as I mentioned this before ,I've done this using interrupt before ,I need to do it using DMA.

Thanks,

Koorosh Hajiani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Do you know why it is not possible?

I tried and tried ,I can only send once however if I place a break point on the actual function and trigger on the chip_select ,It works fine.

I checked registers both SPI and DMA nothing jumps at me.

is there anyone at NXP who could answer this question.is it DMA limitation in regards to DATA BUS being 32 bits in width?

What is it?

Can't be SPI, because I'm sending 40 bits blocking and none blocking.

This is very frustrating.

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The problem is in the integration between SPI and DMA SDK drivers.

The SPI driver expects to receive total number of bytes divisible by bytes per frame for some internal configuration.

The hardware, however, allows this use case.

DMA can transfer 8, 16 and 32 bits at a time.

To send a 40-bit frame, the DMA needs to transfer two 32-bit transfers.

As you can see in the description of TCR register, FRAMESZ bit field,

• If the frame size is larger than 32 bits, then the frame is divided into multiple words of 32-bits; each word is loaded from the transmit FIFO and stored in the receive FIFO separately.

• If the size of the frame is not divisible by 32, then the last load of the transmit FIFO and store of the receive FIFO will contain the remainder bits. For example, a 72-bit transfer will consist of 3 words: the 1st and 2nd words are 32 bits, and the 3rd word is 8 bits.

In case of a 40-bit frame, the transfer will consist of 2 words (64 bits).

The 1th word contains 4 bytes and the 2nd word the 5th byte.

So, the software must align the data.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Based on feedback I got from the SDK team, it is not possible with the SDK drivers. There is still a question whether it is possible with the hardware or not. This is rather a corner use case. I'm investigating it.

Please consider creating a ticket for such a specific request.

How to submit a new question for NXP Support

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thanks for your response,

This would not work for me, I need to be able to communicate to the slave in a continuous basis every 20 ms.

I have this working right now but it is not DMA.

Actually I was able to send 5 bytes continuously using DMA by controlling the chip_select as GPIO having DMA transfer a byte at a time however With this method, it takes longer to transmit data on the bus.

I can send you the project if you're interested.

Thanks,

Koorosh Hajiani