- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Model-Based Design Toolbox (MBDT)

- :

- Model-Based Design Toolbox (MBDT)

- :

- S32K1xx - Low Power Modes Introduction

S32K1xx - Low Power Modes Introduction

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K1xx - Low Power Modes Introduction

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

One of the most important features of the S32K1xx is the power management controller, that allows the user to minimize the current consumption depending on the running application. The PMC blocks allows user to handle the device power modes and trigger subsystems execution when switching between power modes.

The following table describes the power modes for the S32K14x processor:

| Mode | Description |

|---|---|

| RUN | The MCU can be run at full speed and the internal supply is fully regulated, that is, in run regulation. This mode is also referred to as Normal Run mode. |

| HSRUN | The MCU can be run at a faster frequency compared with RUN mode and the internal supply is fully regulated. |

| STOP | The core clock is gated off. There are two variants of stop mode - STOP1 and STOP2. In STOP1 system clock as well as bus clocks are gated. In STOP2 bus clocks keep running whereas system clocks are gated.

|

| VLPR | The core, system, bus, and flash clock maximum frequencies are restricted in this mode. On-chip voltage regulator is in a low power mode that supplies only enough power to run the chip at a reduced frequency.

|

| VLPS | The core clock is gated off. System clocks to other masters and bus clocks are gated off after all stop acknowledge signals from supporting peripherals are valid. Places the chip in a static state with Low Voltage Detect (LVD) operation off. This is the lowest-power mode in which pin interrupts are functional.

|

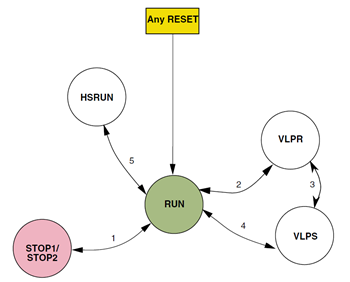

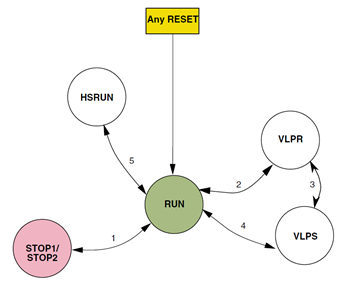

The following diagram shows the power mode transitions. Any reset always brings the chip back to the Normal Run state. In run, stop modes active power regulation is enabled. The VLPR modes offer a lower power operating mode than normal modes. VLPR is limited in frequency.

Power mode state transition diagram (S32K1xx Series Reference Manual, Rev. 4, 06/2017 pag.969)

For more information about power modes and please read the AN5425, Power Management for S32K14x.

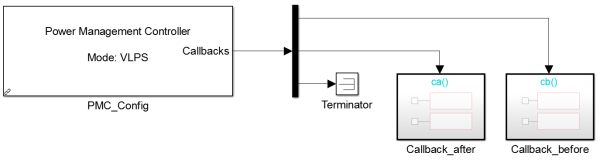

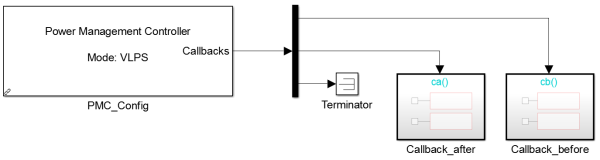

Another important feature that we provide through the new MDBT release is the possibility of automatically call a subsystem "Before", "After" and "Before and after" switching between the power mode selected in the PMC_Config block. The following example shows a PMC_Config block that changes the running mode to VLPS and calls two callbacks: the first one is called "Before" entering the VLPS mode and the second one is called "After" the ISR Handle is executed. The "Before and after" callback is not required so a terminator was added.

PMC_Config Blocks Callbacks example

For demonstrating the functionality of the power management controller we created an application presented in the following video, that measures the ambient temperature using an NXP S32K144 controller. The example combines some blocks in Model-Based Design Toolbox as FLEXIO, LPTMR and PMC.

The peripherals blocks used for this examples, can be found in MBDT and provides the following features:

- FLEXIO is a highly configurable module providing a wide range of functionality including emulation of a variety of serial communication protocols. The MBDT blocks provides support for the following communication protocols: I2C, UART, SPI.

- LPTMR (low-power timer) can be configured to operate as a time counter with optional prescaler, or as a pulse counter with optional glitch filter, across all power modes, including the low-leakage modes. The MBDT blocks provides support to configure LPTMR as Time Counter mode or Pulse Counter mode and an interrupt handler functionality.

- PMC (power management controller) provides multiple power options allowing users to optimize power consumption for the level of functionality needed. The MBDT blocks provides support for running the S32K144 trough the following power modes: VLPS, VLPR, HSRUN, RUN, STOP1/2 and also it can run some callbacks to be triggered on changing the power mode.

On this example the controller uses I2C emulation via FLEXIO to read the temperature from an I2C sensor and send the value over UART communication, every 10 seconds. While the microcontroller waits for those 10 seconds to pass, it runs in the STOP1 low power mode. To wake up the processor every 10 seconds, an interrupt is triggered by the low power timer which is clocked by the SIRC clock. Also to measure the real time current consumption we connected an ammeter in series with the microcontroller on the J15 jumper of the S32K144EVB.

For more detailed explanation please watch the following video.

You can also download and test this example which is available as attachment.

Thank you for your attention! if you have questions feel free to reply to this discussion.

Original Attachment has been moved to: mbdt_s32k14x_pmc_temperature_example.mdl.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am working on Low Power Mode of s32k144, can someone help on Register based to code to do RUN Mode to VLPR Mode to VLPS Mode and back to RUN Mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

I am working on Low Power Mode of s32k144 and for that I am using Example_S32K144_RTC_VLPS_S32DS_ARM_22_v2 code to test low power mode. But I am not able to see any difference in current consumption between normal run mode and low power/stop mode. Please suggest how to test with s32K144 EVK board and share us the latest sample code.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @paneri ,

In this community, we try to answer questions related to the Model-Based Design Toolbox. However, to measure the current that the processor is using, you have to please your Ammeter on the J15. This is bypassed by the R117 resistor.

Have a look on this article here https://community.nxp.com/t5/NXP-Model-Based-Design-Tools/How-to-put-S32K-MCU-into-sleep-low-power-m...

Hope this helps,

Marius

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Marius,

Thanks for the summary provided.

One year later, I was wondering how to use the ARM SYStick together with low power modes. SYStick is always clocked by the core clock, that is stopped in stop2 and VLPS. Furthermore, NVIC is disabled and in AWIC list of peripherals the SYSTICK does not appear.

What's the best practice here?

Thanks and K.R.

L.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Catosh,

Thank you for your interest in the S32K14x controllers. This community is dedicated to the Model-Based Design Toolbox for Matlab and I think that your question is not related to that.

But let me understand your question: are you looking for a way of waking up the processor whenever the SYStick interrupt is triggered? Or you want to set a timer to wake up the processor even from the VLPS and STOP2 running mode? In this case, according to the table Table 38-4. Module operation in available low power modes from the S32K-RM the LPIT/LPTMR/RTC timers are available (only with SIRC as clock source) in Async operation in theVLPS/STOP2, so I would use an interrupt triggered by those peripherals.

I am waiting for your response,

Marius

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Marius,

Sorry, i didn't notice I was posting in the wrong section - I saw that your topic was related to Low power modes and that it somehow was helping me in clarifying the topic.

In ARM architecture the SysTick was thought as a timer for the tick of an operating system or a scheduler, but looks like that SysTick peripheral + OS it's not the best fit for low power designs - at least not on the S32K14x family. Of course, for low power I can choose from the other three clocks but then the SysTick loses its original purpose.

Hence my question, I was wondering if there are some best practices or design guide from NXP in order to leverage both the low power capabilities of the S32K AND the SysTick from ARM architecture.