- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- QorIQ Processing Platforms

- :

- T-Series

- :

- How PBL identifies u-boot location in NOR flash from PBI commands for T1042?

How PBL identifies u-boot location in NOR flash from PBI commands for T1042?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am trying to understand how the PBL is transitioning from PBI instruction into BOOT startup location which reside in NOR FLASH?

Here is the RCW + PBI from the T1042RDB (T1042 Reference Design Board)

e8000000: aa55aa55 010e0100 0c18000e 0e000000 -> RCW preamble

e8000010: 00000000 00000000 86000002 40000002

e8000020: ec027000 01000000 00000000 00000000

e8000030: 00000000 00030810 00000000 01fe580f

e8000040: 00000000 00000000 09250100 00000400 -> PBI commands started at "e800004c" CCSR write 0x0000_0400 to address 0x25_0100

e8000050: 09250108 00002000 08138040 89564dd5 -> CCSR write 0x0000_2000 to address 0x25_0108 and PBI command for CRC check

How the PBI CCSR writes in the above are used to transition into NOR Flash u-boot start address?

Just for additional information, I have included possible relevant snip of the document I have been looking.

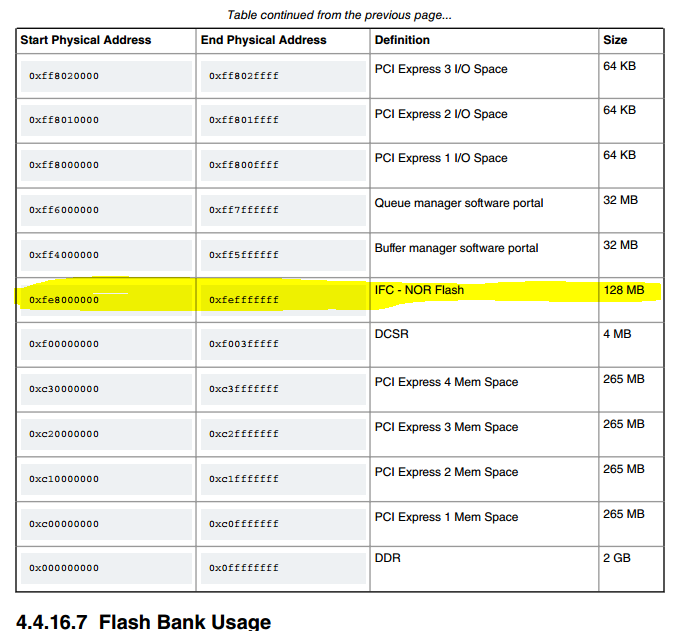

Here is the memory map from the QorIQ SDK v2.0-1701 Documentation document

Page #324 section 4.4.16.6 System Memory Map in this document it specify the memory map as follow:

Table 94. NOR flash memory map in the QorIQ SDK v2.0-1701 document specify the NOR flash as follow:

Thanks,

Anteneh

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The PBI commands represent workaround for the erratum A-007662: For x1 link width, PCIe2 controller trains in Gen1 speed while configured for Gen2 speed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> How the PBI CCSR writes in the above are used to transition into NOR Flash u-boot start address?

There is no relation at all.

Note that mentioned tables show System and NOR Flash memory maps AFTER the U-Boot mapping of the memory space - i.e. after initial booting.

Refer to the QorIQ T1040 Reference Manual, 4.3.3 Boot Space Translation:

"Each core begins execution with the instruction at effective address 0x0_FFFF_FFFC. To get this instruction, the core's first instruction fetch is a burst read of boot code from effective address 0x0_FFFF_FFC0."

In case of NOR Flash booting and reset settings of the eLBC CS0 this corresponds to the last 64 bytes in the NOR Flash device connected to the CS0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ufedor

Is it possible to change internal memory map of Nor flash ? While POR sequence, I wonder how system knows when Nor flash is selected as boot device in RCW, current bank U-boot is located at 0xEFF4_0000 and current bank rcw at 0xE800_0000.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

RCW resides at the offset 0 of the selected Flash memory device/bank.

For U-Boot refer to its sources, for example:

u-boot/README at b3f98d438eefd1b355efdec0b50af5813ff8d0e1 · qoriq-open-source/u-boot · GitHub

u-boot/T104xRDB.h at b3f98d438eefd1b355efdec0b50af5813ff8d0e1 · qoriq-open-source/u-boot · GitHub

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ufedor,

Thank you for your message and pointing out the "QorIQ T1040 Reference Manual, 4.3.3 Boot Space Translation". What exactly this the following CCSR write are doing then?

.....

e8000040: 00000000 00000000 09250100 00000400 -> PBI commands started at "e800004c" CCSR write 0x0000_0400 to address 0x25_0100

......

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The PBI commands represent workaround for the erratum A-007662: For x1 link width, PCIe2 controller trains in Gen1 speed while configured for Gen2 speed.