- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Using the ID acceptance filter MSCAN KEA128?

Using the ID acceptance filter MSCAN KEA128?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm trying to understand how the id acceptance filter for MSCAN works in KEA128, does any one have an idea of how it works?, how the CANIDAR0-CANIDAR3, CANIDMR0-CANIDMR3 registers have to be configured? which logical operator is used where comparing the registers with the id read (or,and,etc)? which result will remain after passing all the filters for an id to be accepted?

I have read section 32.4.5 Identifier acceptance filter, but I don't figure it out how it works.

Regards,

Emilio Moyers

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Emilio,

As you have read section 32.4.5 Identifier acceptance filter in the RM of KEA128, the MACAN receiver is a 5 stage FIFO instead of separate message buffers, there is only one address space for the receiver FIFO, the actual message ID which is received by MSCAN is saved in MSCAN_REIDR0~3 for 29 bits extended ID and MSCAN_REIDR0~1 for 11 bits standard ID.

Regarding the acceptance of filter, there are two bank: fisrt bank and second bank.

The first bank includes the following registers:

MSCAN_CANIDAR0~3

MSCAN_CANIDMR0~3

The second bank includes the following registers:

MSCAN_CANIDAR4~7

MSCAN_CANIDMR4~7

The IDAM bits in MSCAN_CANIDAC define the filter pattern, I copy it here:

"

Identifier Acceptance Mode

The CPU sets these flags to define the identifier acceptance filter organization.

In filter closed mode, no message is accepted such that the foreground buffer is never reloaded.

00 Two 32-bit acceptance filters.

01 Four 16-bit acceptance filters.

10 Eight 8-bit acceptance filters.

11 Filter closed.

"

Assume that you set the IDAM bits as 00 in binary, the "Two 32-bit acceptance filters" pattern filter is used because there are two bank.

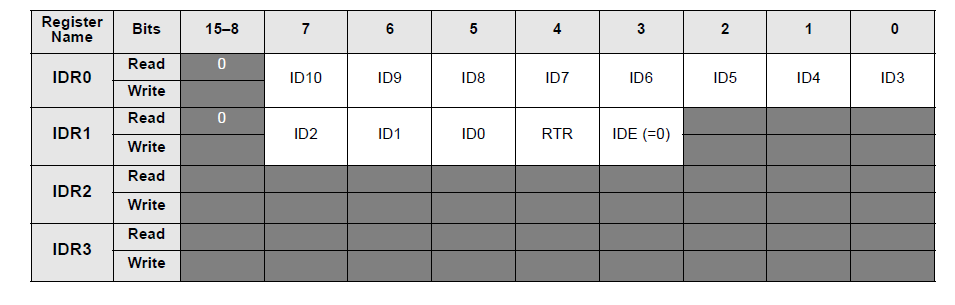

Assume you use 11 bits standard pattern, I think you can use the following pattern for the first/second bank:

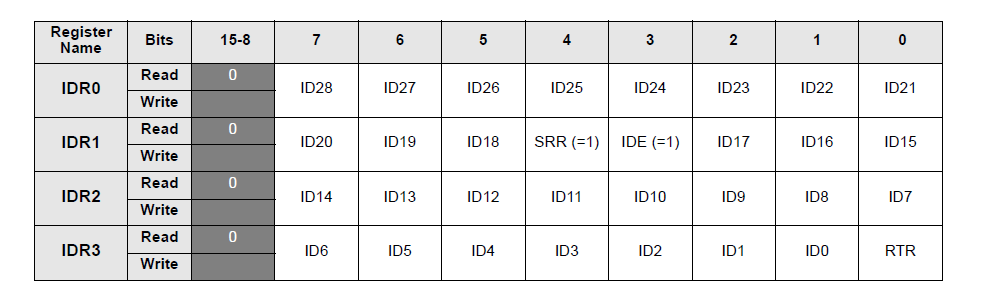

If you use 29 bits extended ID, you can use the following pattern for first/second bank:

I copy the figure from RM of MC56F80x, they are all use MSCAN, the patten is the same.

Hope it can help you.

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Emilio,

As you have read section 32.4.5 Identifier acceptance filter in the RM of KEA128, the MACAN receiver is a 5 stage FIFO instead of separate message buffers, there is only one address space for the receiver FIFO, the actual message ID which is received by MSCAN is saved in MSCAN_REIDR0~3 for 29 bits extended ID and MSCAN_REIDR0~1 for 11 bits standard ID.

Regarding the acceptance of filter, there are two bank: fisrt bank and second bank.

The first bank includes the following registers:

MSCAN_CANIDAR0~3

MSCAN_CANIDMR0~3

The second bank includes the following registers:

MSCAN_CANIDAR4~7

MSCAN_CANIDMR4~7

The IDAM bits in MSCAN_CANIDAC define the filter pattern, I copy it here:

"

Identifier Acceptance Mode

The CPU sets these flags to define the identifier acceptance filter organization.

In filter closed mode, no message is accepted such that the foreground buffer is never reloaded.

00 Two 32-bit acceptance filters.

01 Four 16-bit acceptance filters.

10 Eight 8-bit acceptance filters.

11 Filter closed.

"

Assume that you set the IDAM bits as 00 in binary, the "Two 32-bit acceptance filters" pattern filter is used because there are two bank.

Assume you use 11 bits standard pattern, I think you can use the following pattern for the first/second bank:

If you use 29 bits extended ID, you can use the following pattern for first/second bank:

I copy the figure from RM of MC56F80x, they are all use MSCAN, the patten is the same.

Hope it can help you.

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiangjun,

For example if I only what to pass the messages with the ID 0x55 (standard id), waht do I need to put in the first bank registers (

MSCAN_CANIDAR0~3,MSCAN_CANIDMR0~3)?

Regards,

Emilio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Emilio,

The MSCAN_IDARx register and the MSCAN_RSIDRx register match each other, if you set the received ID as 0x55(the ID bits is 000 0101 0101), and set the IDAM bits as 00, you can set as following:

MSCAN_CANIDAR0=0x0C; //it include ID10~3

MSCAN_CANIDAR1=0xC0 //it includes ID2~0

You can set the MSCAN_CANIDMR0=0xFF; MSCAN_CANIDMR1=0xF8;

It is okay.

Hope it can help you.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hii

- Can you explain the logic behind this masking, its not clear please provide explanation with other examples

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiangjun, with this configuration:

MSCAN_CANIDAR0=0x0C; //it include ID10~3

MSCAN_CANIDAR1=0xC0 //it includes ID2~0

MSCAN_CANIDMR0=0xFF; MSCAN_CANIDMR1=0xF8;

¿which id wold pass the filter? I dont understad the logical operation. In this example:

id 0000 1010 101

dar 0000 1100 1100

dmr 1111 1111 1111

i dont understand, why id 0x55 pass the filter?

Regards,

Julian echeverry