- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- PWM Duty Cycle Issue - Kinetis L ( MKL26Z128 )

PWM Duty Cycle Issue - Kinetis L ( MKL26Z128 )

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PWM Duty Cycle Issue - Kinetis L ( MKL26Z128 )

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Everyone!

I want to use TPM2 timer (Edge-Aligned PWM Mode) as DAC for audio generating. The reason for this solution is that I need more than one channel for my application (simple Wave player and tone generator).

I need at least two channels and I haven't been able to successfully multiplex output of DAC (there is only one channel in MKL26Z128).

Issue:

I've written easy app for generating sine wave with dev kit FRDM-KL25Z (very similar processor). In this application I'm using two timers TPM1 and TPM2:

- TPM1 is used for PWM duty cycle changing with sampling frequency 8 KHz.

- TPM2 is used in Edge-Aligned PWM Mode, counting with frequency c. 93 Khz.

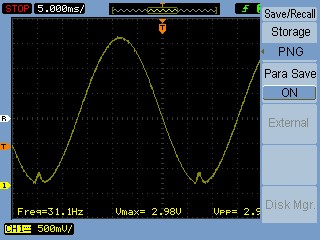

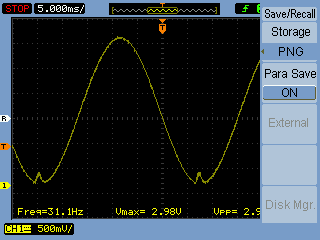

Everything works fine except one state. When I want to set CnV ( PWM compare register ) with value 1, there is unexpected glitch in PWM duty cycle.

PWM duty cycle should be close to 0%, but sometimes instead of 0%, there is PWM duty cycle 100%.

The result of this glitch is shown in figure below.

Also I've attached whole project, where I'm generating sine wave.

In combination with PWM I'm using R C low pass filter (R = 10k, C = 100n). Output of PWM is on pins PTE23 and PTE22.

Are there any rules, for setting TPMx_CnV register? What am I doing wrong?

Ugly, but simple solution to this is instead of 1 set CnV with value 2, but I don't really want this.

Thanks,

Jan

Original Attachment has been moved to: pwm.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jan

There is something strange with the way that the TPM updates the value written to CnV when the value there is already very small.

In edge aligned mode your write won't immediately update the value in the register since this is synchronised to the counter match (that is, the value becomes only valid at the end of the PWM period so that the counter value can't already be higher than the new value, for example).

The problem only occurs when you already have 1 in the CnV register and you write "another" 1 - it is not that there is a 100% duty-cycle period taking place because the error is not large enought (there would be a bigger jump) but the PWM duty cycle value does somehow glitch.

This is possibly an errata that hasn't been reported/documented yet but there is a simple workaround:

Before writing a new value, check whether it is the same as the one already there and if it is, do nothing - then you should find that also writing 1 (which works the first time) when 1 is already there can't disturb.

Therefore, in the routine that is writing the new CnV value do

if (new_value != CnV) {

CnV = new_value;

}

and you should find your sine wave will then be glitch free!!

Note however that this will work in the case of a sine wave with a few values of 1 at the lowest wave crest where the write can be filtered. In the case of code writing 1,2,1,2,1,2 the filtering is not possible and the effect is also seen. Therefore the only complete workaround is indeed to avoid writing the value 1 (or 0) and scale the signal range to be (2..max. + 1), which is also not usually a big deal

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Mark Butcher

I meet the issue like this , KL02Z for PWM Using

When C0V write 1 then Error happened , i has already send this community to Customer and tell them avoid 1 in CnV , solve the issue .but they hope NXP can provide a document to explain this .

Could you provide me Errata document ? and is this issue will make other module error ?

Which other Kinetis parts has the same issue ?

Thanks !!!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

You can get errata from Arm® Cortex®-M0+|Ultra-Low Power Kinetis® KL0x MCUs|NXP but this effect is not included.

I expect that it is present in all Kinetis parts with TPM.

For an official response you could create a service request.

Regards

Mark