- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- imxrt LQFP SDRAM reliability

imxrt LQFP SDRAM reliability

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

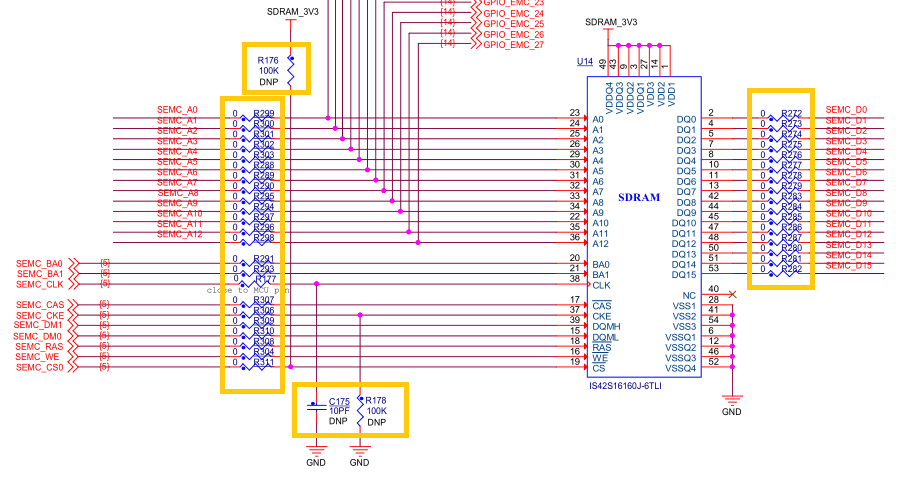

My design use a imxrt1021 in LQFP144 package and a 32MB SDRAM directly connected routed in 2-layer board with good GND plane but with great distance for the plane (due to tickness of 2-layer PCB). This produce impedance mismatch for DQn/Dn/CKx/etc.

The design files is in:

GitHub - martinribelotta/imxrt1020-module: iMX RT 1020 CPU module

In the hardware design manual it advice to put resistors on the pins of data and directions to avoid the reflection of the signals due to impedance mismatching. The dimensions of recommended tracks/vias in the PCB design rules is apparently specified for a 4-layer PCB with standard stackup, not for 2-layer.

But... when I see the refernece design (MIMXRT1020-EVK design files) the series resistors is 0ohm (sheet 12 of the document "SPF-29856_A3.pdf" inner MIMXRT1020-EVK-Design-Files.zip file)

The gerbers in the design package show a bad GND plane and many lines crossing. This is good practice?

Viewing this question:

Is the SDRAM on the 1020 EVK broken?

I have the following doubts:

- Is reliable the routing of 1020 EVK?

- The R0 ohm in serie with data/address/control/clock lines is necesary?

- The absence of good ground plane is problematic?

- In any case... The problems may mitigate dropping down the CLK frecuency of SDRAM?

Many thanks for the time.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

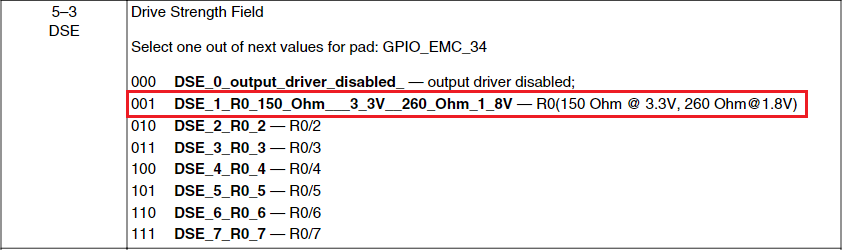

> DSR level 3 strength on the SDRAM drivers. I not localize any reference in RefMan:

drive strength is configured by DSE field of IOMUXC_SW_PAD_CTL_PAD.. register,

for example sect.34.7.171 SW_PAD_CTL_PAD_GPIO_AD_B0_04 SW PAD Control

Register (IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_04) i.MX RT1050 Processor Reference Manual

https://www.nxp.com/docs/en/reference-manual/IMXRT1050RM.pdf

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin

recommended to follow guidelines provided in

Hardware Development Guide for the MIMXRT1050/MIMXRT1060 Processor

https://www.nxp.com/docs/en/user-guide/MIMXRT105060HDUG.pdf

Reference board was designed when not all documentation was prepared so

it may differ from recommendations in Hardware Development Guide.

> problems may mitigate dropping down the CLK frecuency of SDRAM?

yes

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Maybe you refer of this:

https://www.nxp.com/docs/en/nxp/user-guides/MIMXRT1020HDUG.pdf

For mimxrt1020 two layer board route? (section 8: Two (p)layer board design)

Ideally, all this problems have solution in a 4layer standard PCB with basic high speed stackup but the cost increase and the imxrt102x family is designed for low cost design (for a 4 layer board is preferable the imxrt1050/60)

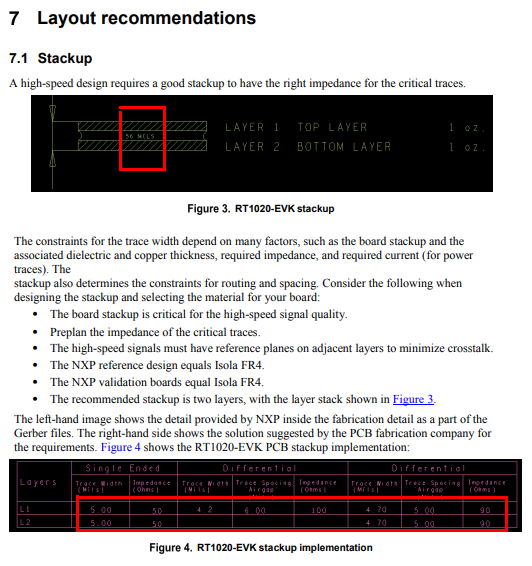

In the section 7.1 (stackup) I cannot calculate the same impedance than the document with standard FR4:

The trace impedance with this dimensions and 56mils of stackup space is 150 ohm in standard FR4 with ER 4.3 if my calculus is right.

I accomplished with all rules in section 7.5 of the same document.

In section 8.4 this recommend said:

Also, it’s found that it needs to lower to SDRAM drive strength to DSR level 3 in software to balance 133MHz R/W speed and board EMC performance.

This paragraph reference to DSR level 3 strength on the SDRAM drivers. I not localize any reference in RefMan:

https://www.nxp.com/docs/en/reference-manual/IMXRT1020RM.pdf

Of this register. Some additional info?

Again, many thanks for your time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> DSR level 3 strength on the SDRAM drivers. I not localize any reference in RefMan:

drive strength is configured by DSE field of IOMUXC_SW_PAD_CTL_PAD.. register,

for example sect.34.7.171 SW_PAD_CTL_PAD_GPIO_AD_B0_04 SW PAD Control

Register (IOMUXC_SW_PAD_CTL_PAD_GPIO_AD_B0_04) i.MX RT1050 Processor Reference Manual

https://www.nxp.com/docs/en/reference-manual/IMXRT1050RM.pdf

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Perfect. I found the rigth way to match impedances on my design.

(from IMXRT1020RM.pdf)