- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- i.MXRT1051DVL6A (A0 silicon): can 3V3 on DCDC_In damage part?

i.MXRT1051DVL6A (A0 silicon): can 3V3 on DCDC_In damage part?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm coming on-board to a new design using the i.MXRT1051DVL6A where the A0 silicon was specified in the BoM and the board was designed with 3V3 on the DCDC-In rail.

Looking in the datasheet, this rail appears to still have an Absolute Maximum rating that seems like it should withstand > 3V0 volts on DCDC-IN, but two boards that I'm working with draw so much current when 3V3 is put on the NVCC-* rails that the LDOs end-up current limiting and shunt the 3V3 rail to about 0.7V.

I've made a small mod where I put a diode in series to the DCDC-IN rail to try and limit it to ~3V but as soon as NVCC is connected the 3V3 rail tanks.

We can't wait for a board spin and are thinking of replacing the BGA MCU using a turnkey but wanted an opinion if 3V3 on A0 silicon will damage the MCU or if we should ensure that hardware mods are performed before powering-up the MCU after replacement.

I've isolated the SDRAM supply and the flash supply is connected to 3V3 directly; all told, it comes down to connecting the NVCC lines to the MCU where the overcurrent happens.

Any thoughts?

Thanks,

Scott Thompson, TC Helicon

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scott

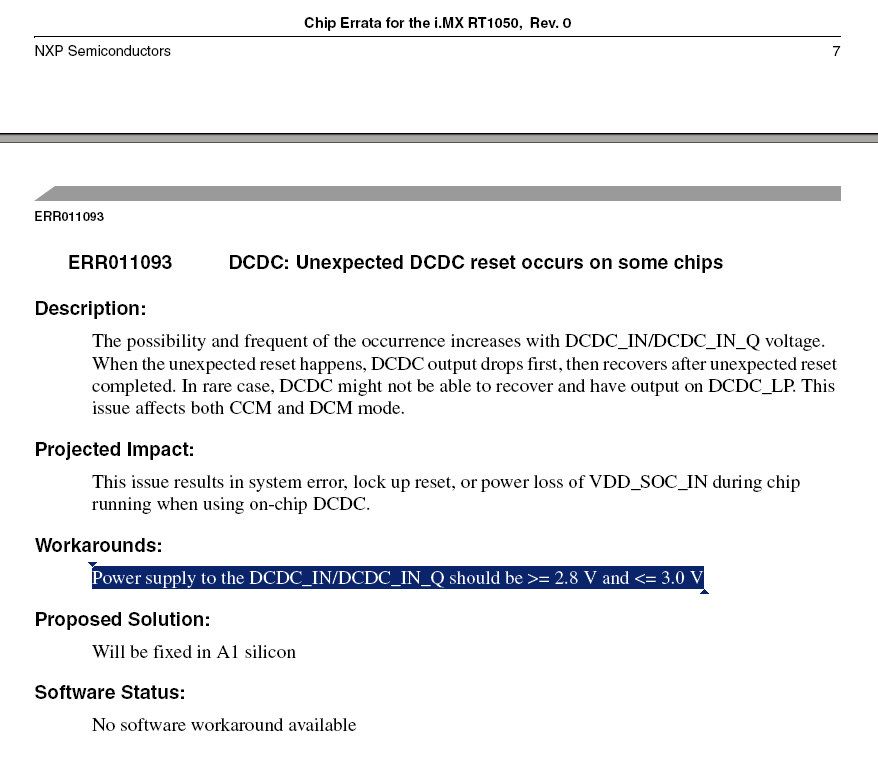

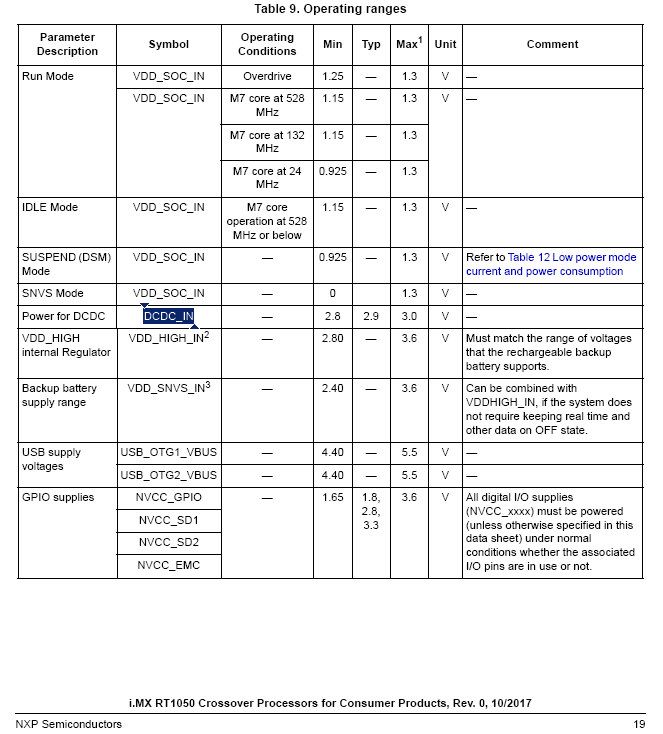

A0 erratum and datasheet (below) limited voltage to 3.0V, so 3V3 may damage chip

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scott

A0 erratum and datasheet (below) limited voltage to 3.0V, so 3V3 may damage chip

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you. I was just coming in to check on the Errata for that mask. Now I have something to hand-wave to. Already have some A1 silicon on order to replace these guys.

Thanks for taking the time to answer my question.

Regards,

Scott Thompson, TC Helicon