- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- SRAM IO refresh failed due to error in RT1175 CM7 core program

SRAM IO refresh failed due to error in RT1175 CM7 core program

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SRAMIO refresh failed due to error in RT1170 CM7 core program,Using SEMC's SDRAM official example program, add their own modified code, make it into SRAM program, SRAMIO refresh in the RT1170 CM7 core program error, run failure.The same program in cm4 core can run normally, want to ask, CM7 core should be configured?Procedural Reference Annex.

#i.MX RT

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @liuhailong ,

Here is SEMC configuration for SRAM 8bit. If you want to use 16bit sram, just set portsize to 16. You should adjust other timing parameters according to your sram.

status_t BOARD_InitSEMC(void)

{

semc_config_t config;

semc_sdram_config_t sdramconfig;

semc_sram_config_t sramconfig;

semc_nor_config_t norconfig;

uint32_t clockFrq = EXAMPLE_SEMC_CLK_FREQ;

/* Initializes the MAC configure structure to zero. */

memset(&config, 0, sizeof(semc_config_t));

memset(&sdramconfig, 0, sizeof(semc_sdram_config_t));

/* Initialize SEMC. */

SEMC_GetDefaultConfig(&config);

config.dqsMode = kSEMC_Loopbackdqspad; /* For more accurate timing. */

SEMC_Init(SEMC, &config);

/* Configure SRAM */

sramconfig.cePinMux = kSEMC_MUXRDY;

sramconfig.address = EXAMPLE_SRAM_START_ADDRESS;

sramconfig.memsize_kbytes = 256 * 1024;

sramconfig.addrPortWidth = 24;

sramconfig.advActivePolarity = kSEMC_AdvActiveLow;

sramconfig.addrMode = kSEMC_AddrDataNonMux;

sramconfig.burstLen = kSEMC_Nor_BurstLen4;

sramconfig.portSize = kSEMC_PortSize8Bit;

sramconfig.syncMode = kSEMC_AsyncMode;

sramconfig.waitEnable = false;

sramconfig.advLevelCtrl = kSEMC_AdvLow;

sramconfig.tCeSetup_Ns = 20;

sramconfig.tCeHold_Ns = 20;

sramconfig.tCeInterval_Ns = 100;

sramconfig.readHoldTime_Ns = 20;

sramconfig.tAddrSetup_Ns = 20;

sramconfig.tAddrHold_Ns = 20;

sramconfig.tWeLow_Ns = 20;

sramconfig.tWeHigh_Ns = 20;

sramconfig.tReLow_Ns = 20;

sramconfig.tReHigh_Ns = 20;

sramconfig.tTurnAround_Ns = 20;

sramconfig.tAddr2WriteHold_Ns = 20;

sramconfig.tWriteSetup_Ns = 20;

sramconfig.tWriteHold_Ns = 20;

sramconfig.latencyCount = 2;

sramconfig.readCycle = 2;

sramconfig.delayChain = 2;

sramconfig.waitSample = 1;

sramconfig.addr27 = kSEMC_MORA27_NONE;

if (SEMC_ConfigureSRAM(EXAMPLE_SEMC, &sramconfig, clockFrq) != kStatus_Success)

{

PRINTF("SEMC SRAM configuration is failed\r\n");

}

EXAMPLE_SEMC->IOCR = (EXAMPLE_SEMC->IOCR & ~(SEMC_IOCR_MUX_CLKX0_MASK | SEMC_IOCR_MUX_CLKX1_MASK)) |

SEMC_IOCR_MUX_CLKX0(2) | SEMC_IOCR_MUX_CLKX1(2) | SEMC_IOCR_CLKX0_AO_MASK;

EXAMPLE_SEMC->IOCR = (EXAMPLE_SEMC->IOCR & ~SEMC_IOCR_MUX_RDY_MASK) | SEMC_IOCR_MUX_RDY(6);

}

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello thanks

According to your description, there are two questions you would like to ask.

1.

EXAMPLE_SEMC->IOCR = (EXAMPLE_SEMC->IOCR & ~(SEMC_IOCR_MUX_CLKX0_MASK | SEMC_IOCR_MUX_CLKX1_MASK)) |

SEMC_IOCR_MUX_CLKX0(2) | SEMC_IOCR_MUX_CLKX1(2) | SEMC_IOCR_CLKX0_AO_MASK;

EXAMPLE_SEMC->IOCR = (EXAMPLE_SEMC->IOCR & ~SEMC_IOCR_MUX_RDY_MASK) | SEMC_IOCR_MUX_RDY(6);What parameters are configured?

sramconfig.cePinMux = kSEMC_MUXRDY;

sramconfig.address = EXAMPLE_SRAM_START_ADDRESS;Haven't the following two lines of code been configured?

2.Do you give CM7 kernel parameters configuration for the program I write?My same code failed in CM4 core, could you tell me what's the difference between MRT1175 CM7 and CM4 core for SRAM? @jingpan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @liuhailong ,

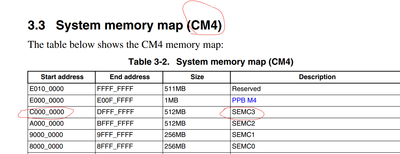

I use SEMC_RDY pin as CE#. Start address is 0x90000000. But you can set to any address from 0x80000000 to 0xe0000000.

There is no difference to CM7 and CM4. You can use cm7 to config SEMC. The result is same.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

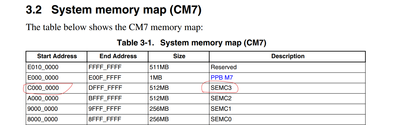

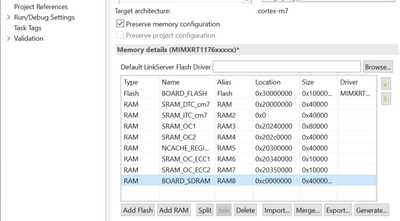

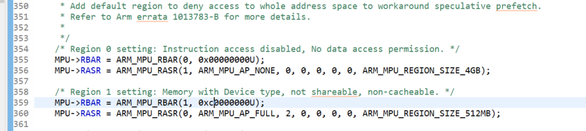

hello,thanksThe first picture shows the configuration of sdram. Please ask if there is a configuration of sdram. The second picture is region 1, but I need to use region 3, SRAM's exclusive region.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1. It's just a name. You can rename it to SRAM or any thing else. Please focus on address.

2. SEMC0~SEMCn belong to SEMC address range.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok my problem solved,can you tell me the reasons that cm4 program does not need to be set,But CM7 has to board.c and settings like that you give me the two pictures?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks a lot