Hello, thank you very much for taking the time to help me with my question, which is related to the previous SEMC SRAM.(Attachment is SEMC CM7 and CM4's own program)

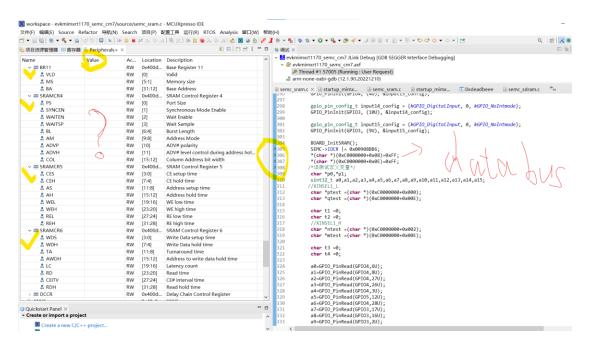

I made changes to the program of the official SEMC SDRAM CM7 core and CM4 core, under the CM7 and CM4 core Source directory, semc\_sdram.c has made changes as semc\_sram.c, All sram content of the code are all the same for cm7 and cm4 program.

The question is: Why can't the CM7 core run with the same program parameters and content and what's the difference between CM7 and CM4 SRAM for SEMC?

1. The desired SRAM bus refresh results can be achieved on the CM4 core. When debugging the breakpoint to the following statement, the SEMC register section will have values and meet the requirements.

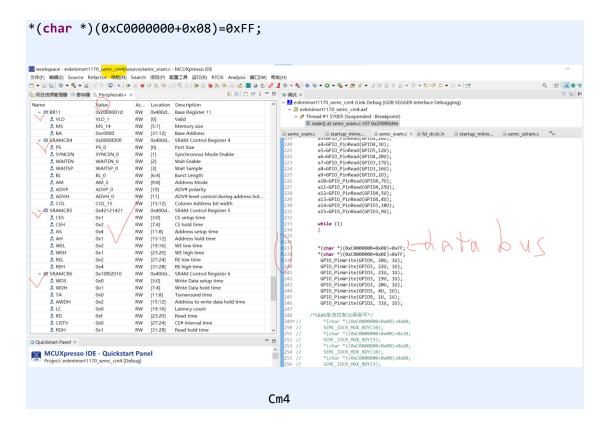

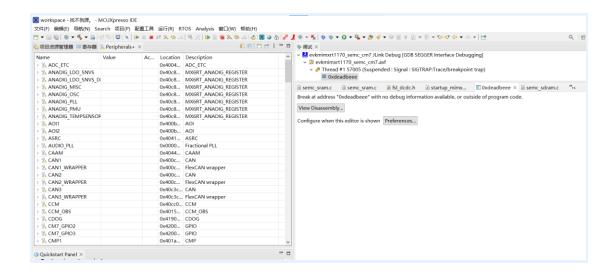

2.CM 7 core will occur when debugging begins.: Break at address "0xdeadbeee" with no debug information available, or outside of program code. And the breakpoint debugs to the same statement when the register value is 0, can not get the expected result

```

*(char *)(0xC0000000+0x08)=0xFF;

```

Cm7