- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- RT1176 SEMC SRAM configuration

RT1176 SEMC SRAM configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RT1176 SEMC SRAM configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The following code is my setup of RT1176 SEMC for 2 x AS6C6416 8MB SRAM, one at address 0x80000000, the other 0x80800000 using ADMUX.

I only seem to be able to write reliably to the first 64 bytes of either SRAM device using a ‘memset((void*)(0x80000000), val, 8*1024*1024)’ command.

I cannot work out the SRAMCR0 register in the SEMC – specifically the COL bits. What does ROW/COL have to do with config of SRAM as mentioned in section 29.3.1.7.1 of the RM? The SRAM is just a linear device. The SEMC_ConfigureSRAMWithChipSelection function just sets this to 12 bits but I do not understand what this relates to.

I have setup IOCR after my call to fix the problem whereby SEMC_ConfigureSRAMWithChipSelection does not configure the CS options correctly.

void InitSEMC()

{

// ## OperationBody [d3982da8-e248-4298-ba70-fb4b1870e3a8]

semc_config_t config;

semc_sram_config_t sramconfig;

uint32_t clockFrq = CLOCK_GetRootClockFreq(kCLOCK_Root_Semc);

/* Initializes the MAC configure structure to zero. */

memset(&sramconfig, 0, sizeof(semc_sram_config_t));

/* Initialize SEMC. */

SEMC_GetDefaultConfig(&config);

SEMC_Init(SEMC, &config);

/* Configure SRAM. */

sramconfig.cePinMux = kSEMC_MUXRDY; /*!< The CE# pin mux setting. */

sramconfig.addr27 = kSEMC_MORA27_NONE; /*!< The Addr bit 27 pin mux setting. */

sramconfig.address = 0x80000000; /*!< The base address. */

sramconfig.memsize_kbytes = 8 * 1024; /*!< The memory size in unit of kbytes. 8MB*/

sramconfig.addrPortWidth = kSEMC_PortSize16Bit; /*!< The address port width. */

sramconfig.advActivePolarity = kSEMC_AdvActiveLow;/*!< ADV# polarity 1: active high, 0: active low. */

sramconfig.advLevelCtrl = kSEMC_AdvLow; /*!< ADV# level control during address hold state, 1: low, 0: high. */

sramconfig.addrMode = kSEMC_AddrDataMux; /*!< Address mode. */

sramconfig.burstLen = kSEMC_Nor_BurstLen1; /*!< Burst length. */

sramconfig.portSize = kSEMC_PortSize16Bit; /*!< Port size. */

sramconfig.syncMode = kSEMC_AsyncMode; /*!< Sync mode. */

sramconfig.waitEnable = false; /*!< Wait enable. */

sramconfig.waitSample = 0; /*!< Wait sample. */

sramconfig.tCeSetup_Ns = 0; /*!< The CE setup time. */

sramconfig.tCeHold_Ns = 0; /*!< The CE hold time. */

sramconfig.tCeInterval_Ns = 0; /*!< CE interval minimum time. */

sramconfig.readHoldTime_Ns = 0; /*!< read hold time. */

sramconfig.tAddrSetup_Ns = 20; /*!< The address setup time. */

sramconfig.tAddrHold_Ns = 0; /*!< The address hold time. */

sramconfig.tWeLow_Ns = 25; /*!< WE low time for async mode. */

sramconfig.tWeHigh_Ns = 0; /*!< WE high time for async mode. */

sramconfig.tReLow_Ns = 30; /*!< RE low time for async mode. */

sramconfig.tReHigh_Ns = 0; /*!< RE high time for async mode. */

sramconfig.tTurnAround_Ns = 10; /*!< Turnaround time for async mode. */

sramconfig.tAddr2WriteHold_Ns = 10; /*!< Address to write data hold time for async mode. */

sramconfig.tWriteSetup_Ns = 0; /*!<Write data setup time for sync mode. */

sramconfig.tWriteHold_Ns = 0; /*!<Write hold time for sync mode. */

sramconfig.latencyCount = 1; /*!<Latency count for sync mode. */

sramconfig.readCycle = 0; /*!<Read cycle time for sync mode. */

sramconfig.delayChain = 0; /*!< Delay chain, which adds delays on DQS clock to compensate timings while DQS is faster than

read data. */

//SRAM1

SEMC_ConfigureSRAMWithChipSelection(SEMC, kSEMC_SRAM_CS0, &sramconfig, clockFrq);

//SRAM2

sramconfig.cePinMux = kSEMC_MUXCSX0; /*!< The CE# pin mux setting. */

sramconfig.address = 0x80000000 + (8*1024*1024); /*!< The base address. */

SEMC_ConfigureSRAMWithChipSelection(SEMC, kSEMC_SRAM_CS1, &sramconfig, clockFrq);

//Fix the driver! Set the IOCTL to correct values for RDY and CSX0 as CS0 and CS1

SEMC->IOCR = SEMC_IOCR_MUX_CSX0(0x08) | SEMC_IOCR_MUX_RDY(0x06);

// ## OperationBody End

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The customer found that the cause of the issue was ADV# polarity, SRAM access appears to be working.

To write in SRAM you might use the SDRAM method used in the SDK example. SRAM addresses are decoded in column/row direction, this is done internally. The default value is 12 but for your specific value, I suggest you contact the memory manufacturer.

CS is not set correctly through SEMC_ConfigureSRAMWithChipSelection(). Configuring directly through the register is suggested.

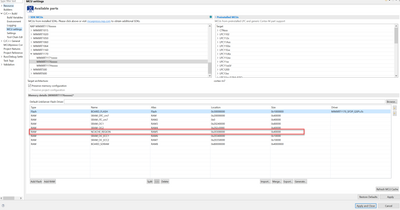

It is important to check your memory details in MCUXpresso to check that non-cacheable mem is not on the SEMC_SRAM region(0x8000_0000):

If you have more questions do not hesitate to ask me.

Best regards,

Omar