- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

RT1176 : Flexspi two octals flash memories and dqs

Hi,

We are developing a new board with two octal flash memories with DQS (data strobe) with a RT1176 processor.

It is possible to use two octal memories on the flexSPI bus with the data strobe signal for each memory ? I have some difficulties to understand the reference manual (i.MX RT1170 Processor Reference Manual, Rev. 1, 05/2021, pagge 2333) on this point.

If yes :

What is the correct pin assignement for DQS pin and chip select pin ?

Example : A_SS0_A and DSQ_A for memory octal A, B_SS0_B and DSQ_B for memory octal B....

What is the flexspi mode ?

Example : COMBINE or PARALLEL. or INDIVIDUAL.

Thank you.

Regards,

Vincent.

Dear @vincent_massonn

Thanks a lot for reaching our technical support. I was assigned to handle your case I am happy to assist you.

Regarding your questions see my answers below:

"It is possible to use two octal memories on the flexSPI bus with the data strobe signal for each memory ?"

--Yes, it is possible.

"What is the correct pin assignment for DQS pin and chip select pin ?"

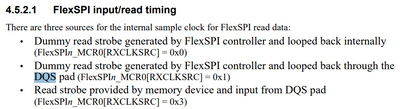

--Please see the picture attached below from Data Sheet about the DQS pins for FlexSPI:

Additionally to this questions, I think that these couple of threads from our community are very helpful to solve your concern:

https://community.nxp.com/t5/i-MX-RT/Can-FlexSPI-DQS-be-ignored/m-p/1522033#M21629

"What is the flexspi mode ? "

--Individual.

Please let me know if you have some additional questions or something more I can help you with.

Sincerely,

Pablo Avalos.