- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: RT1173 JTAG/SWD connection problems

RT1173 JTAG/SWD connection problems

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RT1173 JTAG/SWD connection problems

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

I'm working with an iMX RT1173 on an custom board. We've checked supply voltages and clock signals, all seems to be fine. Also we've compared our schematic against MIMXRT1170-EVK and can't see any major differences in supply, clock or JTAG/SWD. But still I'm not able to connect to CPU with Debugger.

Using Lauterbach yTrace I got message 'Running (Core Power Down)' and DAP: CorePowerDown CTRLSTAT = 0xd0000000 just after command 'SYStem.PowerUp'.

Using Segger JLink I got 3 times "Found SW-DP with ID 0x6BA02477 / Failed to power up DAP" and then "Connection failed.".

I've checked reset lines, reset signal seems to be good. JTAG/SWD itself seems to be working, otherwise the CTRLSTAT bit for 'system power up request' will not be working (I assume). CTRLSTAT register shows missing ack for 'Debug Power Up'.

Can someone give me a hint where the problem can be located?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_ ,

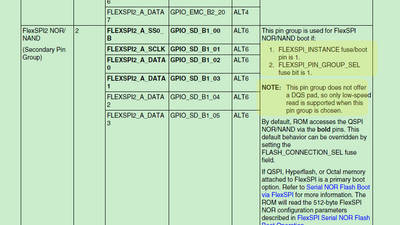

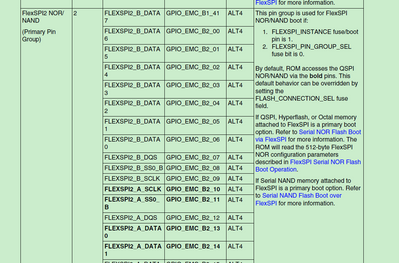

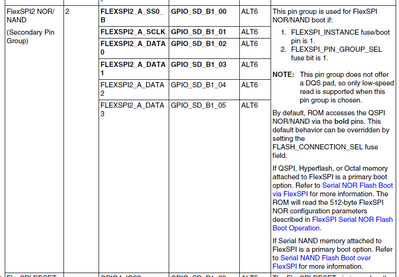

One point need to care, which is ignore previously, it is the flexSPI speed, please use the low speed test it, as the FlexSPI2 NOR secondary pin group doesn't offer DQS pad, so only support low-speed read.

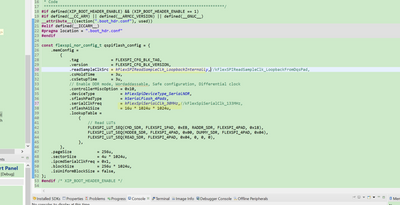

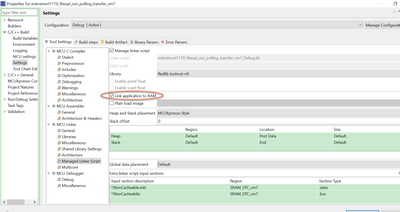

So, please modify the code XIP:

1. app XIP

.seralClkFreq use 30Mhz, just for testing.

DQS loopback internally.

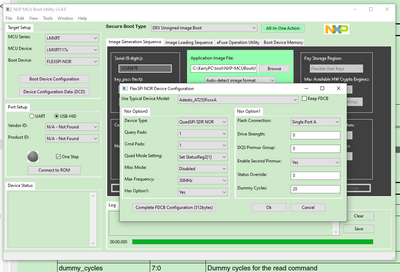

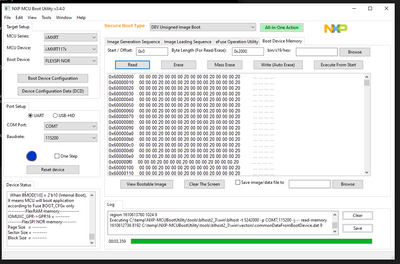

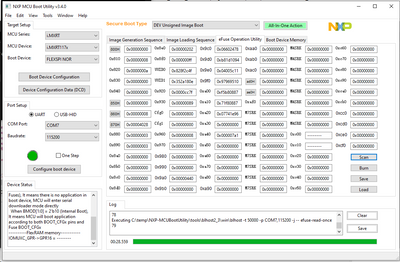

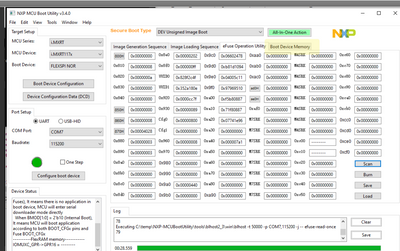

2. MCUbootUtility, please use this configuration to test:

3. Polling code

flexspi_device_config_t deviceconfig = {

.flexspiRootClk = 30000000,

.flashSize = FLASH_SIZE,

.CSIntervalUnit = kFLEXSPI_CsIntervalUnit1SckCycle,

.CSInterval = 2,

.CSHoldTime = 3,

.CSSetupTime = 3,

.dataValidTime = 0,

.columnspace = 0,

.enableWordAddress = 0,

.AWRSeqIndex = 0,

.AWRSeqNumber = 0,

.ARDSeqIndex = NOR_CMD_LUT_SEQ_IDX_READ_FAST_QUAD,

.ARDSeqNumber = 1,

.AHBWriteWaitUnit = kFLEXSPI_AhbWriteWaitUnit2AhbCycle,

.AHBWriteWaitInterval = 0,

};

Please use the low speed and test it again.

Any updated information, please kindly let me know.

best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

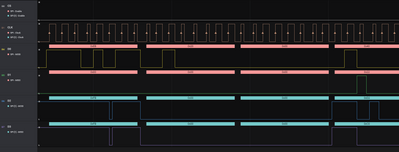

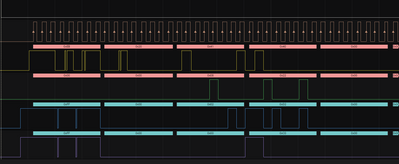

I'm actual in lab and had a close look at the QSPI signals. I can see MCU reading SFDP registers on normal SPI mode with 30MHz clock. Afterwards the status register 2 is read (also with 30MHz normal SPI), chip has onle the quad enabled flag 0x02 set. Up to this point all seems fine.

In the next step an XIP read array command (0xEB) is startet at address 0x001000. So MCU read IVT Table. This access is done with 60MHz as expected cos I've burned 'xSPI_FLASH_FREQ' fuses to value '6'. Strange thing here's that I can see data from flash after 8 dummy cycles but data will start with address 0x001004. According Adesto datasheet the flash has default 2 dummy cycles, so probably the chip sends first 4 bytes while MCU sends dummy cycles.

As you can see in below screenshots the data lines show 0xCD 24 00 as first data.

I've set the autoprobe fuse but propably the autoprobe failes due to slow SPI clock. I've try to set dummy cycles fix to 2 in fuses xSPI_FLASH_DUMMY_CYCLE to see if it helps, otherwise I start with next PCB on monday.

Best Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I've tested the MCU Boot Utility with your settings, but without success. On Logic Analzyser I can see an Read Array command but with starting address 0x001000. The Flash response with data (but here I assume with 1 dummy cylce to mouch, data starts with 0x10 02 but should start with 0xD1 00 20). As you can see in screenshots below there is more or less valid data in QSPI lanes but in data showed in MCU Boot Utility has nothing in common.

I'll go on with changes in polling example.

Best Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_ ,

Dummy cycle is really didn't modified, I find your QSPI flash dummy cycle is 2, and in the FCB, the dummy cycle should be filled with:

FLASH_DUMMY_CYCLES-2So, do you try to input the dummy cyle in the code or the MCUbootUtlity as 0, whether the wave output the correct dummy cycle or not?

I find your MCUBootUtility already can read the data, just the readout data is not correct.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

power sequence look's good except an additional 150ms delay before POR_B due to external reset component in power supply.

We've done some research and it looks like a problem with our flash. We've attach a QSPI Nor Flash at FlexSPI2 (using secondary pin group). After I changed the boot config to serial loader I can access using debugger.

But now I ran into next issues. After serial loader was active I changed fuse bits with MCU Boot Utility, I changed fuses 0x9A0 to 0x00000006 (set FLASH_CONNECTION_SEL to 'PORTB CS0' and FLEXSPI_SPI_GROUP_SEL to 'secondary'). After reboot of device I still can access via JTAG but there is no connection with MCU Boot Utility anymore.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_

So, your used flexSPI pin is not the same as the MIMXRT1170-EVK board, right?

As I know, the debugger download code to the flash also related to the program flashdirver, and this flashdriver will defines the related interface, different debugger the flashdriver file is not the same, I don't have your Lauterbach, so I don't know your related flashdriver code is using which interface.

Now, you can debug the code, I think you can try to download the simple code to the internal RAM, whehter that works, if that works OK, just the flash can't work, then I think still need to check your flash area.

Now, you connect to the flexSPI2 using the following interface?

In fact, when you don't familiar with the chip, we don't recommend you burn the fuse.

You also can try to modify this code and run it in the internal ram, whether your external flash works ok or not?

SDK_2_11_0_MIMXRT1170-EVK\boards\evkmimxrt1170\driver_examples\flexspi\nor\polling_transfer\cm7

You need to change the pinmux the related pin, and the interface, test this code at first.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

according Lauterbach support it should be possible to access QSPI flash at FlexSPI2.

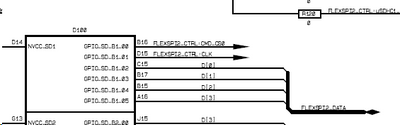

Wr're using 2nd pin group, so correct tabel from TRM should be:

Actual I use a new hardware. Boot mode is set to 'Internal' and no fuses are burned.MCU start to 'Serial Download', I can connect using 'MCU Boot Utility'.

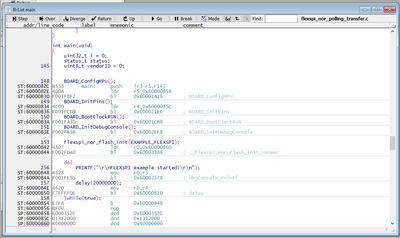

I've managed to change polling transfer example. Debug output shows "FLEXSPI example started!" and "Vendor ID: 0x1" (I think the AT25FF161A has vendor ID 0x1F). Call to function flexspi_nor_enable_quad_mode() won't return. I think there's still no connection to flash.

When I got it right there is no need to change fuse for 2nd pin group to this test, let me know if I had to.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_

Thanks for your effort and the new board without the fuse modification.

1. Which QSPI flash chip you are using now in your own new board? The same as MIMXRT1170-EVK, and just the flexSPI interface is not the same? IS25WP128-JBLE?

As different QSPI, the LUT command may have difference.

2. About the Lauterbach, I am not use your flashdriver firmware can support it, it may normally support the flexSPI1 in the firmware. If you have the Lauterbach flashdriver source code, you can check it.

3. About the MCUbootUtility with new board and can't connect, it should be related to the configuration, as you are using the flexSPI2.

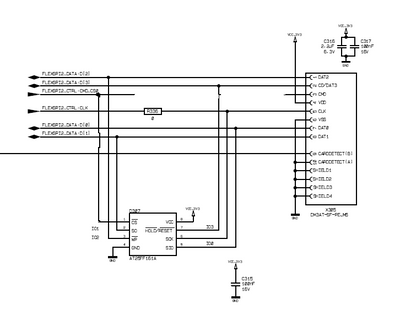

Please share me your flexspi QSPI connection schematic, I need to check it.

4. About polling transfer example, which detail point you have modified, please list all the item which you have modified, I need to check it.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I try to answer your questions as good as possible

1 - We're using Adesto AT25FF161A which is quite simmilar to the AS25SF series.

2 - According Lauterbach Support the flash connection should working, but I'm on to clarify this in parallel.

3 - Here are the schematic part with flash connection. The CS wire is changed to CS0 on my board, actual PCB accidentally connected flash to CS1.

4 - I've added new pins in 'pin configuration' from MCUXpresso. Added used peripherals and updated code with MCUXpresso. Changed definitions EXAMPLE_FLEXSPI, XAMPLE_FLEXSPI_AMBA_BASE, EXAMPLE_FLEXSPI_CLOCK, FLASH_PORT to FlexSPI2. Changed configuration to run from RAM. Generated AXF file is loaded with Lauterbach Debugger. I've added modified project so you can diff it.

I hope this information helps to analyze the problem. If you need further information just let me know.

Best Regards

Stephan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_

Seems you didn't modify the LUT, please modify the LUT like this:

const uint32_t customLUT[CUSTOM_LUT_LENGTH] = {

/* Normal read mode -SDR */

[4 * NOR_CMD_LUT_SEQ_IDX_READ_NORMAL] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x03, kFLEXSPI_Command_RADDR_SDR, kFLEXSPI_1PAD, 0x18),

[4 * NOR_CMD_LUT_SEQ_IDX_READ_NORMAL + 1] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_READ_SDR, kFLEXSPI_1PAD, 0x04, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0),

/* Fast read mode - SDR */

[4 * NOR_CMD_LUT_SEQ_IDX_READ_FAST] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x0B, kFLEXSPI_Command_RADDR_SDR, kFLEXSPI_1PAD, 0x18),

[4 * NOR_CMD_LUT_SEQ_IDX_READ_FAST + 1] = FLEXSPI_LUT_SEQ(

kFLEXSPI_Command_DUMMY_SDR, kFLEXSPI_1PAD, 0x08, kFLEXSPI_Command_READ_SDR, kFLEXSPI_1PAD, 0x04),

/* Fast read quad mode - SDR */

[4 * NOR_CMD_LUT_SEQ_IDX_READ_FAST_QUAD] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0xEB, kFLEXSPI_Command_RADDR_SDR, kFLEXSPI_4PAD, 0x18),

[4 * NOR_CMD_LUT_SEQ_IDX_READ_FAST_QUAD + 1] = FLEXSPI_LUT_SEQ(

kFLEXSPI_Command_DUMMY_SDR, kFLEXSPI_4PAD, 0x06, kFLEXSPI_Command_READ_SDR, kFLEXSPI_4PAD, 0x04),

/* Read extend parameters */

[4 * NOR_CMD_LUT_SEQ_IDX_READSTATUS] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x81, kFLEXSPI_Command_READ_SDR, kFLEXSPI_1PAD, 0x04),

/* Write Enable */

[4 * NOR_CMD_LUT_SEQ_IDX_WRITEENABLE] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x06, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0),

/* Erase Sector */

[4 * NOR_CMD_LUT_SEQ_IDX_ERASESECTOR] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0xD8, kFLEXSPI_Command_RADDR_SDR, kFLEXSPI_1PAD, 0x18),

/* Page Program - single mode */

[4 * NOR_CMD_LUT_SEQ_IDX_PAGEPROGRAM_SINGLE] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x02, kFLEXSPI_Command_RADDR_SDR, kFLEXSPI_1PAD, 0x18),

[4 * NOR_CMD_LUT_SEQ_IDX_PAGEPROGRAM_SINGLE + 1] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_WRITE_SDR, kFLEXSPI_1PAD, 0x04, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0),

/* Page Program - quad mode */

[4 * NOR_CMD_LUT_SEQ_IDX_PAGEPROGRAM_QUAD] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x32, kFLEXSPI_Command_RADDR_SDR, kFLEXSPI_1PAD, 0x18),

[4 * NOR_CMD_LUT_SEQ_IDX_PAGEPROGRAM_QUAD + 1] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_WRITE_SDR, kFLEXSPI_4PAD, 0x04, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0),

/* Read ID */

[4 * NOR_CMD_LUT_SEQ_IDX_READID] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x9F, kFLEXSPI_Command_READ_SDR, kFLEXSPI_1PAD, 0x04),

/* Enable Quad mode */

[4 * NOR_CMD_LUT_SEQ_IDX_WRITESTATUSREG] =//kerry 0X01 ->0X31

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x31, kFLEXSPI_Command_WRITE_SDR, kFLEXSPI_1PAD, 0x04),

/* Enter QPI mode */

[4 * NOR_CMD_LUT_SEQ_IDX_ENTERQPI] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x35, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0),

/* Exit QPI mode */

[4 * NOR_CMD_LUT_SEQ_IDX_EXITQPI] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_4PAD, 0xF5, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0),

/* Read status register */

[4 * NOR_CMD_LUT_SEQ_IDX_READSTATUSREG] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0x05, kFLEXSPI_Command_READ_SDR, kFLEXSPI_1PAD, 0x04),

/* Erase whole chip */

[4 * NOR_CMD_LUT_SEQ_IDX_ERASECHIP] =

FLEXSPI_LUT_SEQ(kFLEXSPI_Command_SDR, kFLEXSPI_1PAD, 0xC7, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0),

};

Your QE bit also need to be modified:

App.h,

#define FLASH_QUAD_ENABLE 0X02//kerry 0x40U->0x02

As the QE bit is the status register 2, bit 1:

https://www.dialog-semiconductor.com/sites/default/files/2022-01/DS-AT25FF161A-182J-112021.pdf

Wish it helps you!

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I've tried with your modifications but still same behavior, output "Vendor ID: 0x1" which is not correct and program stuck in function call "flexspi_nor_enable_quad_mode(EXAMPLE_FLEXSPI);".

I've PCB with attach logic analyzer on QSPI lanes but I can't see any operation on the lines. It seems like the programm dosen't access the SPI flash in any way.

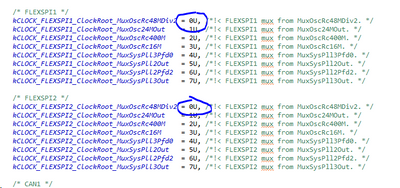

Can you have a look at "flexspi_clock_init()", I'm not sure with the call to "CLOCK_SetRootClockMux()".

Best Regards

Stephan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_ ,

Thanks for your information.

If your flexSPI2 even don't have the wave, it means, the code still not work, still need to check the flexSPI detail modification, maybe something is lost.

About CLOCK_SetRootClockMux(), please check the details, whether it configure the flexSPI2 clock, at least the flexspi2 should have clock out.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I've checked the clock MUX values, but according given documentation the value should be right:

Meanwhile Lauterbach Support was able to get flash working with uTrace Debugger. I've done some short tests and it seems to be working, so it looks like the problem is not located on PCB. I think there is still some modification missing in example project, but have no glue where...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_

Thanks for your updated information.

1. About the flexspi2 clock configuration, you are correct:

static inline void flexspi_clock_init(void)

{

/*Clock setting for flexspi1*/

CLOCK_SetRootClockDiv(kCLOCK_Root_Flexspi1, 2);

CLOCK_SetRootClockMux(kCLOCK_Root_Flexspi1, 0);

/*Clock setting for flexspi2*/

CLOCK_SetRootClockDiv(kCLOCK_Root_Flexspi2, 2);

CLOCK_SetRootClockMux(kCLOCK_Root_Flexspi2, 0);

}

/* Configure FLEXSPI2 using OSC_RC_48M_DIV2 */

rootCfg.mux = kCLOCK_FLEXSPI2_ClockRoot_MuxOscRc48MDiv2;

rootCfg.div = 1;

CLOCK_SetRootClock(kCLOCK_Root_Flexspi2, &rootCfg);

The API will help to configure the flexSPI2.

When you test the polling code, you run it in RAM?

2. Lauterbach Support was able to get flash working with uTrace Debugger

Please give me some debug screenshot, whether the flash address is correct? I mean, whether your code is downloaded to the external flash or not?

If it can download code to the flash, whether boot works or not after you modify the fuse:

1). FLEXSPI_INSTANCE fuse/boot pin is 1.

2). FLEXSPI_PIN_GROUP_SEL fuse bit is 0.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

my test programm is running in RAM, I've use the setting you described in screenshot.

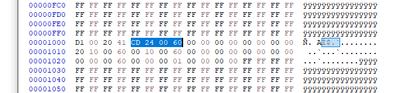

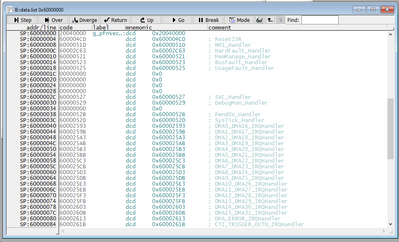

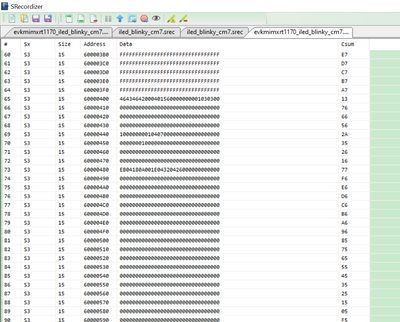

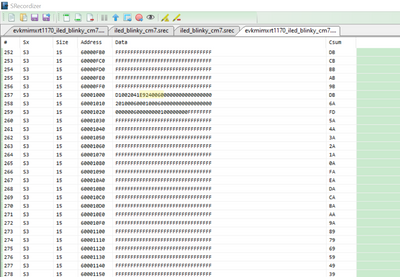

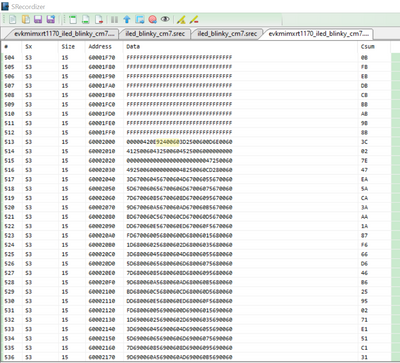

According the flashed code, when try to run from flash I use 'release' configuration in MCUXpresso. With Lauterbach I load axf file which write program code to flash. When I dump the first addresses from flash it look like this:

I've set fuses as follows:

We're using 2nd pin group, so there is FLEXSPI_PIN_GROUP_SEL set to 1.

I've opened another thread about generation bootable binary file (Create bootable image for RT1173 QSPI flash - NXP Community), so I think we can stick to 'run from RAM' configuration and try to get polling example working.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_

1. Seems your Lauterbach already enter the debug mode, please run it directly.

Then check the printf information, whether the external QSPI flash runs OK or not?

You can see the printf information through the UART interface.

GPIO_AD_25->LPUART1_RXD

GPIO_AD_24->LPUART1_TXD

2. MCUBootUtlity, seems you also connect to the chip, please select bootDevice Memory

In the Boot Device Memory, you can readout the memory.

In the connection area, you can select One Step to connect your board.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

as already stated in comment above I'm able to run the modified polling example and get some output on debug port but with wrong manufaturer ID and program stuck at "flexspi_nor_enable_quad_mode(EXAMPLE_FLEXSPI);".

MCU Boot Utility can connect to MCU but is not capable to access QSPI Flash at FlexSPI2 (2nd pin group). I'm already in contact with NXP FAE but there is still no solution.

Best Regards

Stephan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_ ,

Thanks for your information, as I don't have the RT1170 board which connect the QSPI in the flexSPI2, so I can't test it direct.

Now, seems only your debugger Lauterbach can download the code, but I find your downloaded code is not correct, it didn't contains the FCB, IVT, so the image is totally wrong, could you please use my attached led_blinky and test it with your Lauterbach?

My image is correct:

From 0X600004000 FCB:

0X60001000 IVT:

From 0X60002000, app:

Please use your debugger test my .axf, whether the led code function works or not? Test it in the internal boot mode directly.

Any updated information, kindly let me know.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i've tried your blinky AXF. Unfortunately I've no access to pin M13 on my board, I've an LED on R10, but not yet managed to get an blinky work with this pin.

Nethertheless, when I program your AXF and reboot in 'internal Boot' configuration I can't access with Debugger (Core Power Down), so it seems MCU Bootloader can't load image. Also MCU Boot Utility have no access.

I've managed to get an binary image from MCU expresso with IVT and FCB. Not sure why, but after changing BOARD_FLASH from 0x3000000 to 0x6000000 in the Release linke file the following lines are missing:

/* Image Vector Table and Boot Data for booting from external flash */

.boot_hdr : ALIGN(4)

{

FILL(0xff)

. = 0x400 ;

__boot_hdr_start__ = ABSOLUTE(.) ;

KEEP(*(.boot_hdr.conf))

. = 0x1000 ;

__boot_hdr_ivt_loadaddr__ = ABSOLUTE(.) ;

KEEP(*(.boot_hdr.ivt))

. = 0x1020 ;

__boot_hdr_boot_data_loadaddr__ = ABSOLUTE(.) ;

KEEP(*(.boot_hdr.boot_data))

. = 0x1030 ;

__boot_hdr_dcd_loadaddr__ = ABSOLUTE(.) ;

KEEP(*(.boot_hdr.dcd_data))

__boot_hdr_end__ = ABSOLUTE(.) ;

. = 0x2000 ;

} >BOARD_FLASH

After adding manual and switch off managed linker files in project configuration I got a binary with FCB and IVT. The binary is attached, so you can have a quick look if you find an error. I got same behavior with your and mine binary file. In 'internal Boot' the MCU won't start. In 'Boot from Fuses' the MCU will go into Serial Download.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Stephan_ ,

You are right, that's why my previous reply share you the code project, which I also add the FCB, IVT in the ld file.

Now, I checked your generated .bin, it is the correct app which contains FCB, IVT, app.

I mean, use your debugger Lauterbach , as previous reply, you can use it download code to the 0X60000000, so whether you can use Lauterbach download the new complete app.bin which contains FCB and IVT?

Best Regards,

Kerry