- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- RT1170 SEMC wait pin

RT1170 SEMC wait pin

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using RT1170 on my board, and I connect SRAM device on SEMC.

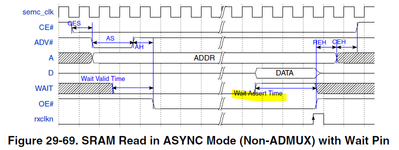

When I use SEMC as ASYNC Mode with Wait Pin, how can I configure "Wait Assert Time" value?

Is it fixed at 3 clocks?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Eugene3,

I believe I understand your inquiry now. Thank you for the clarifications.

The Wait Assert Time is not configurable. It measures the time between the WAIT signal being asserted and the SEMC's sampling of the data from the SRAM. As you can see, once the data was sampled, the SEMC does not care about the WAIT signal.

This sampling is determined by the rxclkn, which is an internal signal that is used by the peripheral to sample the SRAM data. The diagram shows that as soon as the data was sampled, OE# is de-asserted. In other words, both the Wait Assert Time assertion and the de-assertion of OE# depend on rxclkn (which is not configurable and therefore neither are these signals in this case).

That said, we can consider that the time it takes for the SEMC to see the wait assert and sample the data (the Wait Assert Time) will be around 3 semc_clk cycles, yes. As soon as the data was sampled, the wait signal is irrelevant and the OE# will be de-asserted.

I hope this clears things up.

BR,

Edwin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Eugene3,

I believe I understand your inquiry now. Thank you for the clarifications.

The Wait Assert Time is not configurable. It measures the time between the WAIT signal being asserted and the SEMC's sampling of the data from the SRAM. As you can see, once the data was sampled, the SEMC does not care about the WAIT signal.

This sampling is determined by the rxclkn, which is an internal signal that is used by the peripheral to sample the SRAM data. The diagram shows that as soon as the data was sampled, OE# is de-asserted. In other words, both the Wait Assert Time assertion and the de-assertion of OE# depend on rxclkn (which is not configurable and therefore neither are these signals in this case).

That said, we can consider that the time it takes for the SEMC to see the wait assert and sample the data (the Wait Assert Time) will be around 3 semc_clk cycles, yes. As soon as the data was sampled, the wait signal is irrelevant and the OE# will be de-asserted.

I hope this clears things up.

BR,

Edwin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you I understand.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Eugene3,

As mentioned on this reply from my colleague on a similar community post, the WAIT signal is handled by the SRAM side, so please look into your SRAM's datasheet for information about how to configure the WAIT signal time to ensure assertion of the data. The Reference Manual only mentions the restriction that the wait valid time must be at least 2 semc_clk cycles.

BR,

Edwin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @EdwinHz

I know the wait signal comes from SRAM side.

When will SEMC de-assert OE# pin after the wait pin is de-asserted by SRAM?