- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- RT1062 timestamping clock (ts_clk)

RT1062 timestamping clock (ts_clk)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As part of a PTP implementation, on the RT1062, I would like to change the timestamping clock from 25MHz to 100MHz.

The reference manual IMXRT1060RM Rev 2, 12/2019 page 2137 section 41.6.94 "Time-Stamping Clock Period Register" mentions the clock period of the timestamping clock in the INC field.

However, I can not find where I can set the source frequency for the this clock.

It is currently set to 25MHz, which appears to be the same as the Ethernet clock. Are the two clocks one and the same?

My question: How can I change the frequency of the timestamping clock?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @zt

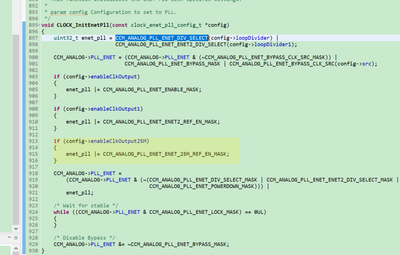

This code is used to configure the timestamping clock:

void BOARD_InitModuleClock(void)

{

/* Set 50MHz output clock required by PHY, set PTP clock 25MHz. */

const clock_enet_pll_config_t config = {.enableClkOutput = true, .enableClkOutput25M = true, .loopDivider = 1};

CLOCK_InitEnetPll(&config);

/* Output 50MHz clock to PHY. */

IOMUXC_EnableMode(IOMUXC_GPR, kIOMUXC_GPR_ENET1TxClkOutputDir, true);

}

25Mhz.

Wish it helps you!

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Kerry, for your prompt reply.

The code snippet you included sets up the Ethernet clock to be 50MHz, which is as expected.

However, I am interested in having the PTP 1588 timestamping clock run at 100MHz.

When I change the .loopDivider from 1 to 2, for example, the Ethernet interface is no longer correctly initialised.

It seems to me that the Ethernet clock and the timestamping clock are linked when they should be independent of each other - am I correct?

There is a missing piece to this puzzle.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @zt ,

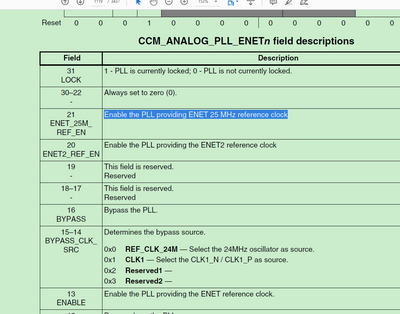

My understand is, if the enableClkOutput25M is enabled, the PTP clock is 25M.

And the 50Mhz output clock is output to the PHY, if you set it to 100Mhz, then the output 100Mhz to the PHY, but your PHY is fixed to use 50Mhz.

This is my understanding, you also can check the RM related register in my above picture.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @zt

This code is used to configure the timestamping clock:

void BOARD_InitModuleClock(void)

{

/* Set 50MHz output clock required by PHY, set PTP clock 25MHz. */

const clock_enet_pll_config_t config = {.enableClkOutput = true, .enableClkOutput25M = true, .loopDivider = 1};

CLOCK_InitEnetPll(&config);

/* Output 50MHz clock to PHY. */

IOMUXC_EnableMode(IOMUXC_GPR, kIOMUXC_GPR_ENET1TxClkOutputDir, true);

}

25Mhz.

Wish it helps you!

Best Regards,

Kerry