- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: RT1060 SEMC PSRAM CLK

RT1060 SEMC PSRAM CLK

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RT1060 SEMC PSRAM CLK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

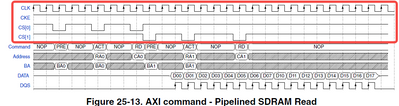

RT1060 RM shows that the CLK of SEMC SDRAM is continuously generated, regardless of whether CS takes effect.But the CLK of SRAM in SYNC mode is only generated when CS is low. Is the actual situation the same as described in the Figure 25-63? SRAM interface will not generate CLK when CS is high?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Hope you are well.

You´re correct, the SEMC CLK will behave as the figures describe.

If you have more questions do not hesitate to ask me.

Best regards,

Omar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Omar

thanks for your reply.

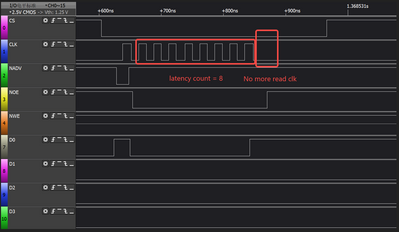

I have validated SEMC SRAM SYNC mode behavior in RT1064 too, it's indeed the same as the figures describe. But I noticed that SEMC CLK disappear after latency count when SEMC reads. if SEMC reads more data in one burst, the last CLK also disappears. The SEMC CLK count is correct when it writes. I want to know if this behavior is normal?

Best regards!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

The CLK should not disappear when reading. There might be an issue with your device or the SEMC configuration.

It will be helpful if you share your SEMC configuration as well as the part number of the memory you are using.

If you have more questions do not hesitate to ask me.

Best regards,

Omar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

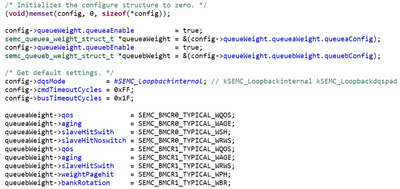

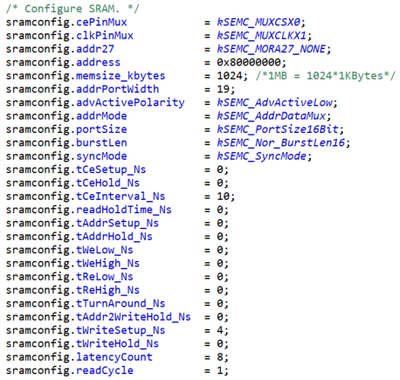

The SEMC basic configuration is default.

The SEMC SRAM configuration is as follows.

The RT1060 doesn't connect to external memory, I just want to know SEMC PSRAM behavior.

Best regards!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It´s hard to tell that this is an expected behavior while no PSRAM memory is connected to the module. The default configuration seems correct but this may vary across different memories.

To check that the read behavior of the module is correct you need to connect a memory to the module.

If you have more questions do not hesitate to ask me.

Best regards,

Omar