- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi,

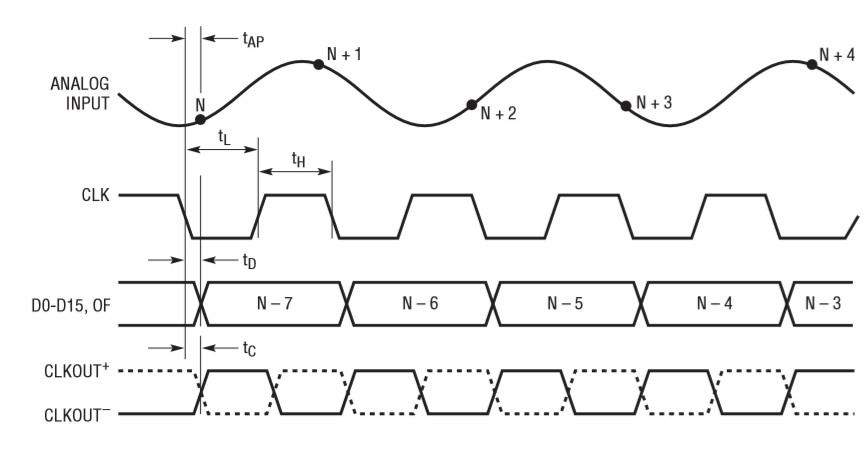

I would like to communicate with pipeline ADC using RT1052, the interface is parallel digital output. just like following timing diagram. All the data bits are synchronized with clk, It should sample the dates on the raising edge of the clk.

My demand:

The maximum clk frequency is 20Mhz.

16bits or 8bits data width.

Continuously buffer at leat 1k data from ADC with maximum 20Mhz frequency, and store the data in the SDRAM.

I am confused how to achieve that. Should I use CSI interface or Flexio interface?

What example is the closest one that I can refer?

Another questions from RT1052 reference manual about FLEXIO interface.

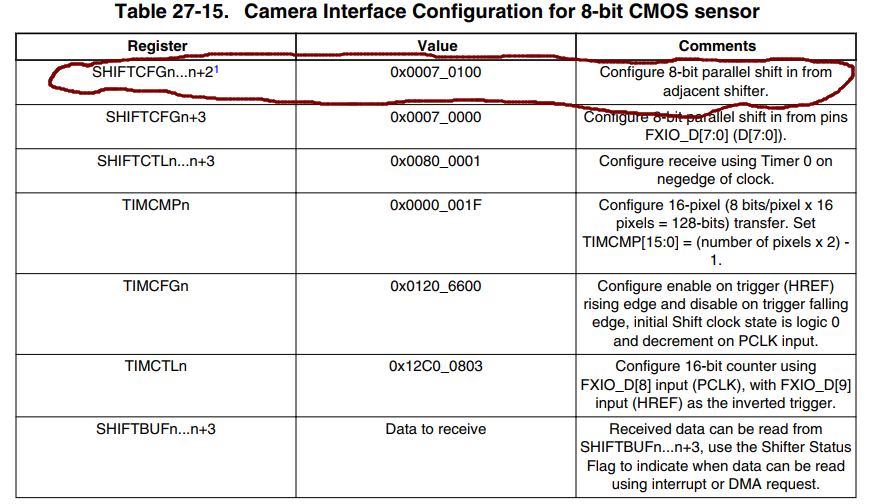

The manual set an example for 8bits CMOS sensor application using FLEXIO parallel interface.

I did not quite understand about it, what's the purpose of configuring SHITER0,1,2 to adjacent shiter?

And how to use DMA work with flexio interace, is there any example?

Thanks a lot for your support.

已解决! 转到解答。

Hello wang Hua,

maybe AN5313 can help you. It shows how to implement 8080 parallel bus interface.

https://www.nxp.com/doc/AN5313

Kind regards,

Stefan