- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: LPSPI with GPIO as Chip Select and Changing CPOL / CPHA (i.MXRT1050/1160)

LPSPI with GPIO as Chip Select and Changing CPOL / CPHA (i.MXRT1050/1160)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm working with an application that runs on a i.MXRT1050 and 1160 with a custom LPSPI driver. I use GPIOs for the chip select pins.

Unluckily, I have two SPI devices connected, that use different CPOL settings. So I have to switch these settings between the transfers. With GPIOs as chip select, I first set the GPIO and then start the transfer via TCR / TDR. Due to that, the idle level of the clock line changes after the chip is selected and the device chip interprets that as a clock.

Is there a possibility to manually set the idle level of the SPI clock line between two SPI transfers without doing a whole byte of dummy transfer?

With kind regards

Christian

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @christian_mauderer,

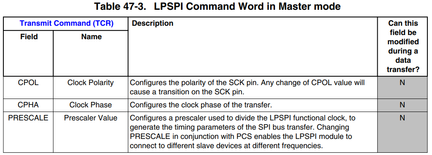

Unfortunately, there is not possible to manually set the idle level of the SPI clock line between transfers without doing a whole byte of dummy transfer. As mentioned in the i.MX RT1050 Processor Reference Manual, the CPOL bit cannot be modified during a data transfer:

[Table 47-3. LPSPI Command Word in Master mode]

Kind regards, Raul.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @christian_mauderer,

Unfortunately, there is not possible to manually set the idle level of the SPI clock line between transfers without doing a whole byte of dummy transfer. As mentioned in the i.MX RT1050 Processor Reference Manual, the CPOL bit cannot be modified during a data transfer:

[Table 47-3. LPSPI Command Word in Master mode]

Kind regards, Raul.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @RaRo,

thanks for your response. It's what I assumed. I'll find a way to work with it.

With best regards

Christian Mauderer