- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- IMXRT1064 HyperRAM Configuration Issue

IMXRT1064 HyperRAM Configuration Issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IMXRT1064 HyperRAM Configuration Issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dear Authorized,

I am trying to configure and use HyperRAM over FlexSPI in my custom board which includes RT1064 and 6KS512SDABHV030.

I am using evkimxrt1064_flexspi_hyper_flash_polling_transfer SDK example by applying Mount and DNP required pin in the readme.txt.

But the example returns 7001 status code after "flexspi_nor_hyperbus_read_cfi" function. I can't get the issue.

I followed up and applied official direction in below document:

https://www.nxp.com/docs/en/nxp/application-notes/AN12239.pdf

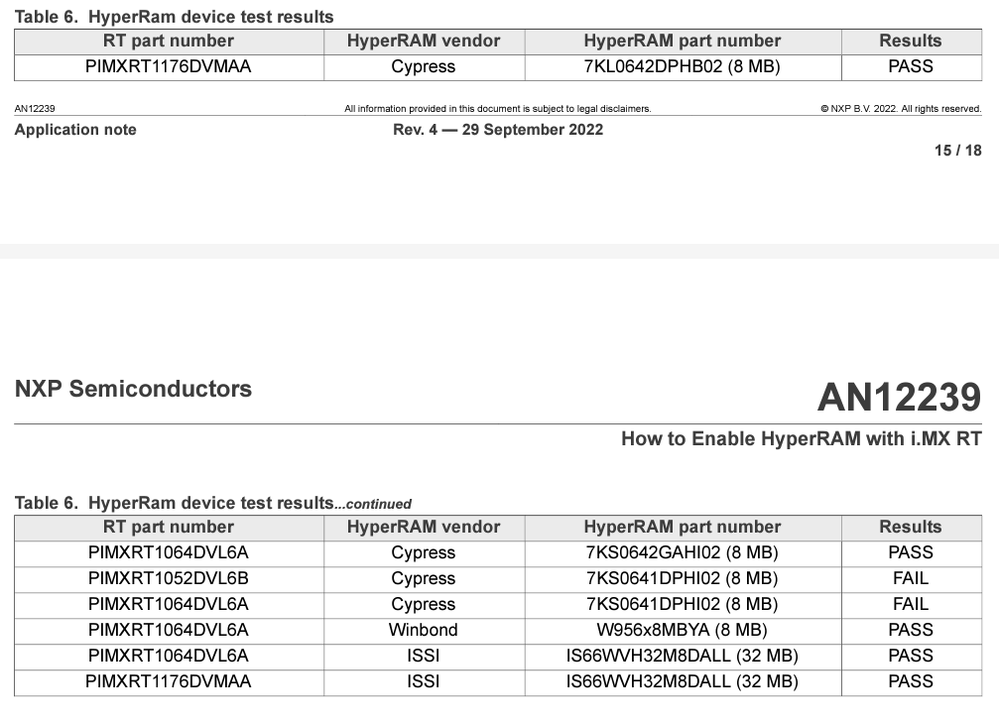

One things that makes me suspicious is below image.

According to above image which is a part of AN12239 doc, some of the Hyperrams are failed. Why? Is there possible to same issue happened for 6KS512SDABHV030. Or is there something that I miss during configuration?

What is the problem related with? Could you please help me?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear @kerryzhou, @Pavel_Hernandez , @Omar_Anguiano

There are some missing points for using HyperRAM with FlexSPI on RT1064. This example code and application note is not enough.

How should I design LUT?

How should I refer to the differences between 1050 and 1064 ?

I tried to configure my own example by using reference 1050 code by building it on flexspi_hyper_flash_polling_transfer SDK example. But it is not successfull.

Is there a deterministic guide?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The LUT should be designed according to the specific commands from the memory datasheet. Here are some examples were customers modified the LUT table to work with the custom device.

Read Id using flex SPI on QPI mode - NXP Community

How to Enable Debugging for FLEXSPI NOR Flash (nxp.com) Chapter 5.4.1.1

There should not be significant changes from RT1050 to RT1064 since the FlexSPI is very similar.

Some HyperRAM devices, such as 7KS0641DPHI02, seem to have an issue in the test. The failed devices enter a hard fault when enabling read prefetch of FlexSPI. When there is a prefetch abort in the middle of command/address cycle, these failed devices seem to have an issue. To avoid the issue, prevent the prefetch abort during command/address cycle. The prevention is hard to implement for FlexSPI. Therefore, it is not recommended to use these failed HyperRAM on i.MX RT series.

Best regards,

Omar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear @Omar_Anguiano ,

Thank you so much for your help. Could you please correct me if I have any miss understanding?

I can use HyperRAM in my custom board by configuring LUT according the memory datasheet? Also, it is enough to use "evkmimxrt1064_flexspi_hyper_flash_polling_transfer" sdk example as base for HyperRAM. I only will configure LUT and things going on.

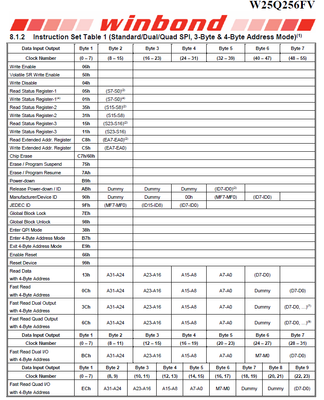

I also examine the first link you shared. The memory which is used by that people have some specific commands to configure LUT commands. It has a instruction set table like below, but I am using S27KS0641DPBHV020 and it has not a Instruction Set Table. I am curios about whether the LUT Instruction like Read Status (0x05), Write Enable (0x05), Erase Sector (0x20) and etc. are universal codes or not ? I get this values from default SDK example of evkmimxrt1064_flexspi_hyper_flash_polling_transfer.

Thanks and Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

LUT instruction may vary depending on the memory. I cannot assure you that instructions like Read Status (0x05), Write Enable (0x05), and Erase Sector (0x20) will be available on all memories under the same index.