- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT

- :

- Re: IMXRT1050 SWD connection repeats CPU halt

IMXRT1050 SWD connection repeats CPU halt

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

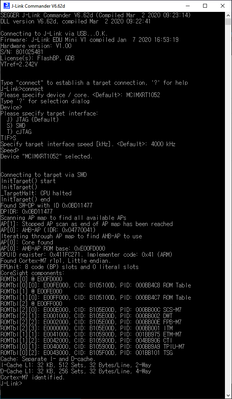

I made a custom iMXRT1050 board very similar to i.MX RT1050-EVKB board. I have checked all the power supplies and clocks and they were all good.

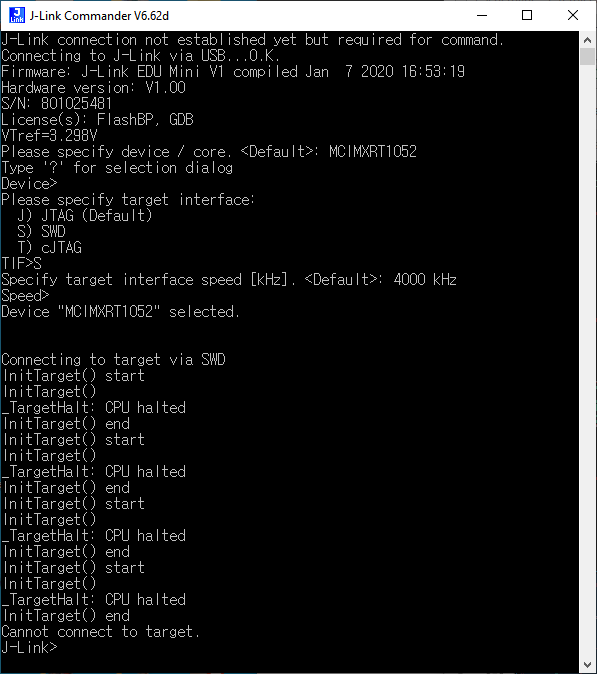

When I tried connecting to EV board with J link, everything works. But, when I try to connect to my custom board, it gives me an error like below.

My VTref is right on 3.3V target, so I'm not sure what's causing this problem.

I saw a similar post here, but there's no problem with my SWD VDD Pin.

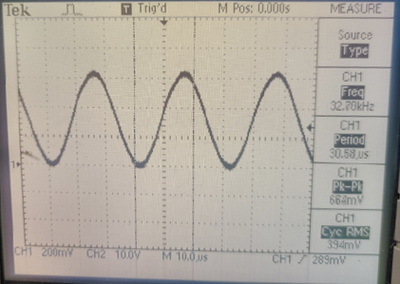

RTC CLK

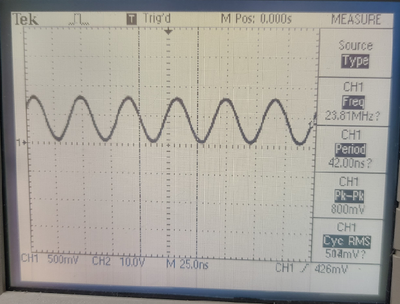

XTAL

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for your reply.

1)Is there a timing graph or table for each power supply?

-- Please check the below figure.

Hope this is clear.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

I think I need to get more information prior to figuring the issue out, so I need you to clarify the below inquires.

1) Does the issue happen on multiple boards?

2) Is the flashloader tool able to contact the target board after forcing the RT1060 to enter the Serial Download mode?

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi jeremy,

Thanks for the feedback. I have checked several boards and they all behaved the same. So, I don't think this is a manufacturing problem, but rather a design problem.

Sharing more details, please check the attached Schematic of i.MXRT1050 of my board. I'm completely new to the iMXRT1050 and I tried to make my board as similar as EVB as possible.

I'm currently not using any flash memory. I'm just using the same SDRAM that was used in the EVB. And you can see in the attachment, I don't think I can force the RT1050 to go to the serial download mode, since there's no adjustable boot mode selection pin available.I didn't know about using HW boot mode selection, so it's not ready on our board.

Is there anything I can try with the current schematic?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

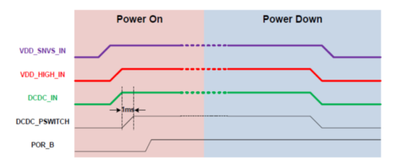

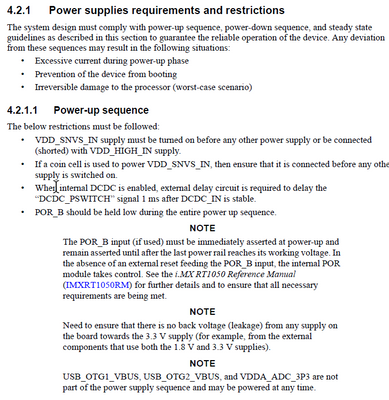

According to the schematic of your board, we can't get an overview of the power-up sequence, and I guess that the issue is related to the power-up sequence, as RT1xxx needs to follow the power-up sequence restrictions which is illustrated below.

So please check it.

Have a great day.

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

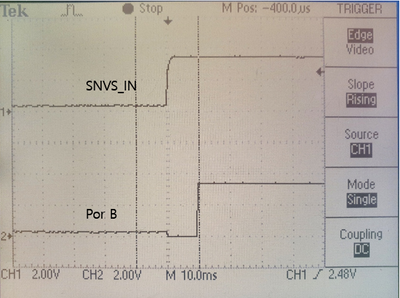

Hi Jeremy,

I checked the power sequences today and the SNVS supply is turned on at the beginning

Por B pin is held low for 10ms and the rest of the power comes on in between.

Is there a timing graph or table for each power supply? I wanted to check if there were any specific delay times for each power supply, but I couldn't find any in the RM.

I also read that pulling up JTAG_MOD pin high can cause trouble for SWD connection, so I removed my pull-up resistor on the GPIO_AD_B0_08 pin, but it didn't make any changes.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for your reply.

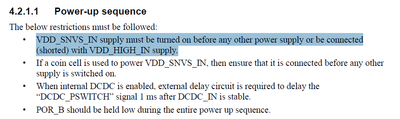

1)Is there a timing graph or table for each power supply?

-- Please check the below figure.

Hope this is clear.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jeremy,

Thank you so much for your help. I got JLink to connect to my board after delaying VDD_High_IN power up just a little. I thought VDD_SNVS and VDD_High timing could be the same because the datasheet said that VDD_SNVS can be shorted to VDD_High.

Anyway now it works, while VTref value seems to be little low though.