- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

IMXRT: Trailing clocks at end of FlexSPI access?

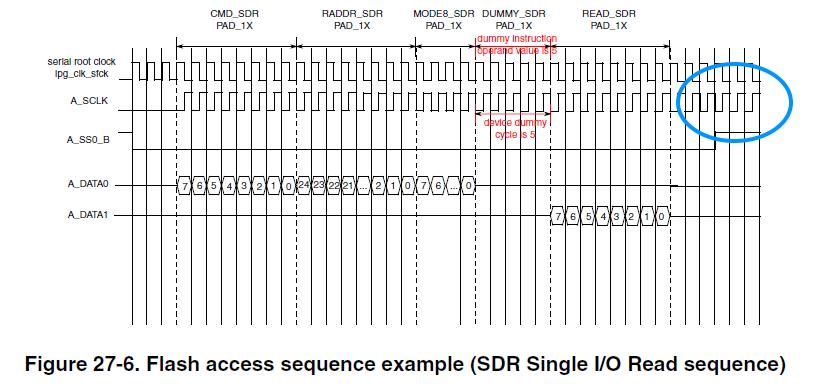

The docs for the FlexSPI controller say that the output SPI clock is turned off when the interface is idle. Timing diagrams, though, show the clock continuing off the right edge of the picture after the end of a transaction.

How many additional clock cycles (if any) can I be guaranteed to get after the transaction is over? I'm interfacing to an FPGA with no PLL so I'll need those clocks.

Example timing diagram from page 1642 of the i.MX RT1060 Reference Manual:

Hello Neil,

Hope you are doing well.

I am confirming with our team to check if this is a mistake or if in fact there is an expected behavior.

I will update you as soon as I have an answer for you.

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

To add a small additional note: several of the other example timing diagrams, particularly the ones for Hyperflash transfers, do *not* show additional cycles after chip select goes away. I wonder if it's simply a mistake in the above diagram?

If I *want* some extra clocks after the data transfer I should just be able to add a DUMMY command right before the STOP command in my read and write sequences, right?

Hello Neil,

Hope you are doing well.

I have received confirmation, that this is an error in the diagram. The FlexSPI controller won't toggle the clock signal beyond the negation of the chip select. We've let the documentation team know this needs to be corrected.

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------