- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: Hard fault for 75% DTCM occupied

Hard fault for 75% DTCM occupied

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Goodmorning,

I'm using a iMXRT1064 with SDK 1.11 and MCUExpresso 11.6.0.

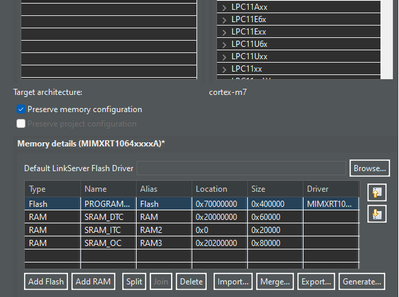

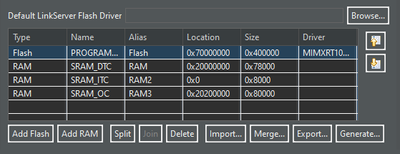

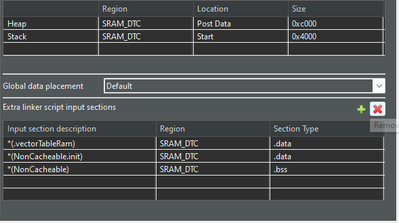

The memory configuration is:

The memory occupation is the following:

Memory region Used Size Region Size %age Used

PROGRAM_FLASH: 555596 B 4 MB 13.25%

SRAM_DTC: 274208 B 384 KB 69.73%

SRAM_ITC: 21328 B 128 KB 16.27%

SRAM_OC: 26 KB 512 KB 5.08%

If I move the data from OCRAM (about 5% occupation) to DTCM (about 70% occupation) the program crashes. If I leave the data in OCRAM the program runs perfectly.

The data that occupies 26kB is a single array of struct.

What are the possible reasons why the program crashes despite not having overflow 100% of memory occupation?

In attachment the .map file of my project.

Thank you.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Davidino ,

The FlexRAM settings seems fine. I also test on my board, it can work. I can write data to 0x20077000, but can't write to 20079000. So, it works.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @jingpan ,

thank you for your answer.

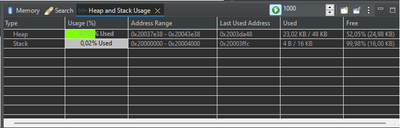

Below you can find the stack and heap usage in the working project, at full operation:

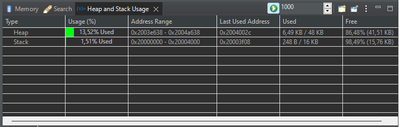

And here the stack and heap usage in the NOT working project, when the error triggers:

If the problem was the stack overflow, I think that it would be visible here.

Since the project is very complex, I propose an hypothetichal cause for the error.

Following the link: https://community.nxp.com/t5/i-MX-RT/How-to-reconfigure-the-flexRAM-on-i-mxRT-1062-using-MCUXpresso/... , I reconfigured the FlexRam in run time with the following modifications and below I highlight the most significant changes:

The code at startup is:

__attribute__ ((section(".after_vectors.reset")))

void ResetISR(void) {

// Disable interrupts

__asm volatile ("cpsid i");

/* Reallocating the FlexRAM */

__asm (".syntax unified\n"

"LDR R0, =0x20003fff\n" // load initial value to stack pointer into R0

"MSR MSP,R0\n" // re-initialize stack pointer by new value

"LDR R0, =0x400ac044\n" // Address of register IOMUXC_GPR_GPR17

// Modificato rispetto all'originale per rispettare la configurazione via eFuses

//"LDR R1, =0x5AAFFAA5\n" // FlexRAM configuration DTC = 256KB, ITC = 128KB, OC = 128KB

//"LDR R1, =0xAAAFFAAA\n" // FlexRAM configuration DTC = 384KB, ITC = 128KB, OC = 0KB

"LDR R1, =0xEAAAAAAA\n" // FlexRAM configuration DTC = 480KB, ITC = 32KB, OC = 0KB

"STR R1,[R0]\n"

"LDR R0,=0x400ac040\n" // Address of register IOMUXC_GPR_GPR16

"LDR R1,[R0]\n"

"ORR R1,R1,#4\n" // The 4 corresponds to setting the FLEXRAM_BANK_CFG_SEL bit in register IOMUXC_GPR_GPR16

"STR R1,[R0]\n"

...

And the MPU configuration is:

/* Region 0 setting: Instruction access disabled, No data access permission. */

MPU->RBAR = ARM_MPU_RBAR(0, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_NONE, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_4GB);

/* Region 1 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(1, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

/* Region 2 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(2, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

#if defined(XIP_EXTERNAL_FLASH) && (XIP_EXTERNAL_FLASH == 1)

/* Region 3 setting: Memory with Normal type, not shareable, outer/inner write back. */

MPU->RBAR = ARM_MPU_RBAR(3, 0x70000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_RO, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_4MB);

#endif

/* Region 4 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(4, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 5 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(5, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_32KB); // ITCM

/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512KB); // DTCM

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512KB); // OCRAM

/* Region 8 setting: Memory with Normal type, not shareable, outer/inner write back */

//MPU->RBAR = ARM_MPU_RBAR(8, 0x20280000U);

//MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512KB);

/* Region 11 setting: Memory with Device type, not shareable, non-cacheable */

MPU->RBAR = ARM_MPU_RBAR(11, 0x40000000);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_4MB);

/* Region 12 setting: Memory with Device type, not shareable, non-cacheable */

MPU->RBAR = ARM_MPU_RBAR(12, 0x42000000);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1MB);

/* Enable MPU */

ARM_MPU_Enable(MPU_CTRL_PRIVDEFENA_Msk);

/* Enable I cache and D cache */

SCB_EnableDCache();

SCB_EnableICache();

...

If you think that this changes are fine, I close the topic as it's too difficult via chat to examine anything.

Thank you in advanced.

Regards,

Davidino

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Davidino ,

The FlexRAM settings seems fine. I also test on my board, it can work. I can write data to 0x20077000, but can't write to 20079000. So, it works.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @jingpan ,

thank you for your answer and confirmation. For the moment I found a work-around using OCRAM, in the future I'll dig deeper what may be the cause of the problem.

Thank you again.