- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT

- :

- Choosing between ITCM and DTCM on IMXRT

Choosing between ITCM and DTCM on IMXRT

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I believe that ITCM can be used for R/W variables as well as code. Similarly DTCM be used for code as well as R/W variables. I assume that code, (and const data?), should be placed in ITCM and R/W variables should be placed in DTCM. Is there a simple guide that illustrates why this is so? I'd be interested to know why R/W variables shouldn't be put in ITCM or why code shouldn't be put in DTCM.

Thanks

John

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi John

> Is there a simple guide that illustrates why this is so? I'd be interested to know why R/W variables shouldn't be put in ITCM or why code shouldn't be put in DTCM.

The best performance is achieved by placing the instruction in ITCM and the data in DTCM.

Cortex-M7 is equipped with a superscalar. Because of this, Cortex-M7 partially processes instructions simultaneously. Therefore, ITCM and DTCM have different I / F bit widths and numbers.

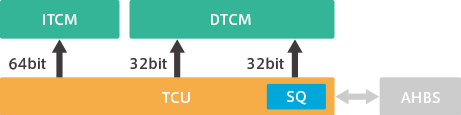

The connection between ITCM, DTCM and CPU (TCU) is as follows:(The access bit width of ITCM is 64 bit * 1, and the access bit width of DTCM is 32 bit * 2.)

If you want to know more info, Please confirm "Arm Cortex-M7 Processor Technical Reference Manual 5.8. TCM interfaces.(http://infocenter.arm.com/help/index.jsp?lang=en)

RM describes that

The Prefetch Unit (PFU) can fetch instructions from any of the TCM interfaces. The Load Store Unit (LSU) and the AHBS interface can each read and write data using any of the TCM interfaces. Best performance is achieved if code is placed in ITCM and data in DTCM. However, there is no functional restriction in which TCM, code and data is placed.

Best Regards,

T.Kashiwagi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi John

> Is there a simple guide that illustrates why this is so? I'd be interested to know why R/W variables shouldn't be put in ITCM or why code shouldn't be put in DTCM.

The best performance is achieved by placing the instruction in ITCM and the data in DTCM.

Cortex-M7 is equipped with a superscalar. Because of this, Cortex-M7 partially processes instructions simultaneously. Therefore, ITCM and DTCM have different I / F bit widths and numbers.

The connection between ITCM, DTCM and CPU (TCU) is as follows:(The access bit width of ITCM is 64 bit * 1, and the access bit width of DTCM is 32 bit * 2.)

If you want to know more info, Please confirm "Arm Cortex-M7 Processor Technical Reference Manual 5.8. TCM interfaces.(http://infocenter.arm.com/help/index.jsp?lang=en)

RM describes that

The Prefetch Unit (PFU) can fetch instructions from any of the TCM interfaces. The Load Store Unit (LSU) and the AHBS interface can each read and write data using any of the TCM interfaces. Best performance is achieved if code is placed in ITCM and data in DTCM. However, there is no functional restriction in which TCM, code and data is placed.

Best Regards,

T.Kashiwagi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Takashi

Thank you for this answer. I understand this a bit better now. I'm

getting used to where to find information, between NXP and ARM documents.

Best Regards

John Aldridge

John Aldridge CEng MIET - Senior Design Engineer - Direct: +44 1903 737353

- Fax: - E-Mail: JAldridge@parker.com

Parker Hannifin Manufacturing Ltd - Electromechanical & Drives Division

Europe - New Courtwick Lane ? Littlehampton? West Sussex, UK ? BN17 7RZ

Phone.: + 44 (0)1903 737000 - Fax: + 44 (0)1903 737 123

Parker Hannifin Manufacturing Ltd - Registered in London no 4806503

Registered Office - Parker House ? 55 Maylands Ave ? Hemel Hempstead ? HP2

4SJ ? United Kingdom