- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- ADC ETC Issues

ADC ETC Issues

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm working with the ADC_ETC module on the IMXRT1176 and using the SDK eaimxrt1176_sdk_2_11_1_2022-05-16 and have run into a couple of issues I need clarified.

1 ) I enable the DONE0 interrupt for Trig 0. I noticed, when I placed a breakpoint in the ISR, that sometimes the DONE0 flag for Trig 0 is set but sometimes it is not. I make sure to clear the flag when exiting the ISR but it seems to re-enter almost immediately. I'm toggling a GPIO and noticed that the GPIO is never set slow. Or it's at least set low for a very small amount of time.

Trig 0 is triggered by the PIT at a rate of 1kHz. If I toggle the GPIO only when the flag is active, then I can see the GPIO toggling at 1kHz as expected.

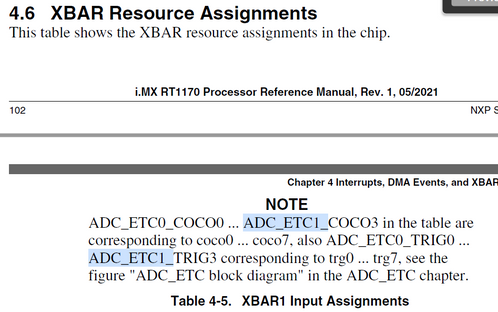

2 ) I wanted to route the output of the PIT to Trig 0 and Trig 4 but noticed that there is no output signal for Trig 4. There is only ADC_ETC0_COCO0, ADC_ETC0_COCO1, ADC_ETC0_COCO2, ADC_ETC0_COCO3, ADC_ETC0_COCO, ADC_ETC1_COCO0, ADC_ETC1_COCO1, ADC_ETC1_COCO2, ADC_ETC1_COCO03.

Does this mean that Trig 4 through 7 for ADC 2 cannot be triggered independently? In order to trigger Trig 4 I had to synchronize it with Trig 1, but there maybe applications where it's desirable to assign priority between these two. It's also inferred in the Reference Manual that I should be able to trigger 4 through 7 independently.

3) There's one small issue with the SDK: Members ADCHCRegisterSelect and ADCChannelSelect of adc_etc_trigger_chain_config_t are not correctly named. The former selects the LPADC HW trigger, the latter selects the associated LPADC command. The comments for these are not correct either.

Thank you

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @rnicolls ,

ADC_ETC0_TRIG0 ... ADC_ETC1_TRIG3 corresponding to trg0 ... trg7, see the figure "ADC_ETC block diagram" in the ADC_ETC chapter.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've been using the RT1062 ADC_ETC, and I expect the signal naming might be similar. The XBAR signal name for the ADC_ETC COCO associated with TRIG4 is ADC_ETC1_COCO0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the reply. I thought as much but didn't get any conversions back from Trig 4 when I used ADC_ETC1_COCO0. I think there must be some other issue with how I've set it up.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1) Did you place the define SDK_ISR_EXIT_BARRIER at the end of the ISR? ARM errata 838869 could be your issue or another DONE0 interrupt is enabled in the ADC-ETC chain config and you are not clearing it (or your other settings are incorrect see 2)?

2) Are you sure you want to connect the PIT -Trigger signal to the ADC-ETC Conversion Complete signals? Does not sound correct for me. Maybe your are looking for the XBAR output signals like ADC_ETC_TRIG00 to ADC_ETC_TRIG13 (which are the ADC-ETC triggers 0 to 7)?

3) sorry don't know your used IMXRT part. Maybe it is different for it but for the 1020 and 1050 series the second one selects the adc channel that should be converted and the first one selects the HC-register to use so the comment would be correct in this case.

Kind regards,

Steve

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the reply.

It seems that ARM errata 838869 is the cause of the issue I'm seeing.

Sorry if it was unclear, but I am using the XBAR output signals to trigger the conversion. I just can't find the one's associated with triggers 4 to 7. I tried using ADC_ETC1_TRIG0 but that doesn't seem to trigger the conversion.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @rnicolls ,

ADC_ETC0_TRIG0 ... ADC_ETC1_TRIG3 corresponding to trg0 ... trg7, see the figure "ADC_ETC block diagram" in the ADC_ETC chapter.

Regards,

Jing