- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi,

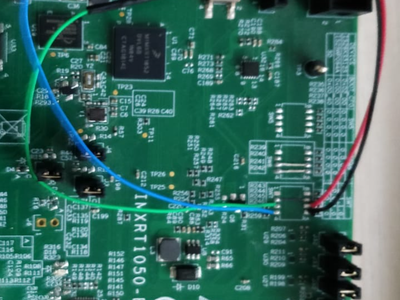

We are using evaluation board IMXRT1050-EVKB and trying to boot from the secondary FlexSPI pins:

| GPIO_AD_B1_08 |

| GPIO_AD_B1_09 |

| GPIO_AD_B1_10 |

| GPIO_AD_B1_11 |

| GPIO_AD_B1_12 |

| GPIO_AD_B1_13 |

| GPIO_AD_B1_14 |

| GPIO_AD_B1_15 |

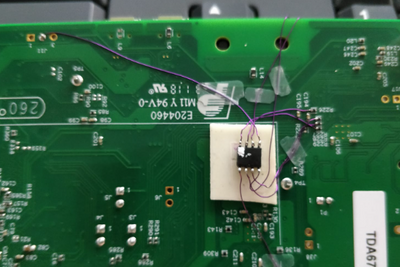

We soldered a Flash to those pins:

Our board's configuration:

BOOT_MODE[1:0]= 10 (internal boot)

BOOT_CGG[10:8]= 111

Why does the internal boot still occur from Flash U33 (primary pins) and not from the secondary pins?

Should we do something else besides the HW setup I have mentioned?

已解决! 转到解答。

Hi @sapirbuz ,

As your connection is still the flexspi 1 A port, just the secondary pinout option for FlexSPI serial NOR flash boot.

So the address still the same from 0X60000000.

Wish it helps you!

Best Regards,

Kerry

Our flash is IS25LP080D-JNLE-TR

datasheet:

https://eu.mouser.com/datasheet/2/198/issi_s_a0003474186_1-2271392.pdf

For now, we have 2 flashes connected to our board: U33 and our external flash (IS25LP080D-JNLE-TR).

For U33, the flash base address is defined as the following:

#define NOR_FLASH_START_ADDRESS (20U * 0x1000U)

What is the base address of the secondary pins flash?

How can we program our external flash?

Hi @sapirbuz ,

As your connection is still the flexspi 1 A port, just the secondary pinout option for FlexSPI serial NOR flash boot.

So the address still the same from 0X60000000.

Wish it helps you!

Best Regards,

Kerry