- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: lan8720 (RMII) with imx6Q(L3.0.35_4.1.0)

lan8720 (RMII) with imx6Q(L3.0.35_4.1.0)

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

lan8720 (RMII) with imx6Q(L3.0.35_4.1.0)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

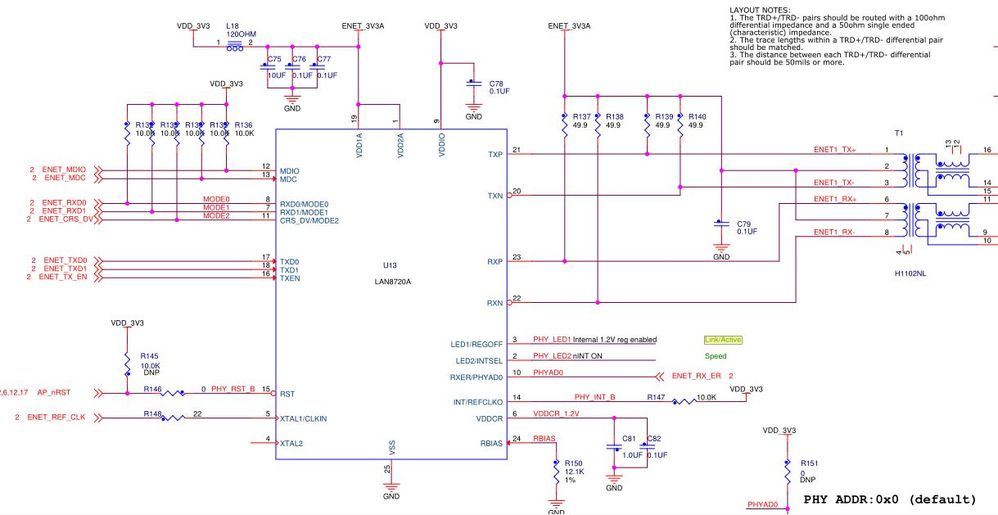

I connected a lan8720 (RMII) with imx6Q. We use the GPIO 16 as clock output for the phy.

i used the following the patch to my kernel.

Re: iMX6 RGMII + ENET_REF_CLK/ENET_TX_CLK

But in both of uboot and kernel , the phy does not work and the link led also does not light.

because the RST pin of lan8720a on our board is connected with POR_B of imx6 control ,

it can't not be set to GPIO. i use soft reset to reset phy.

Here is my iomux config:

board_mx6q_XXX.h file

----------------------------------------------------------------------

/* ENET */

MX6Q_PAD_ENET_MDIO__ENET_MDIO,

MX6Q_PAD_ENET_MDC__ENET_MDC,

MX6Q_PAD_ENET_RXD0__ENET_RDATA_0,

MX6Q_PAD_ENET_RXD1__ENET_RDATA_1,

MX6Q_PAD_ENET_CRS_DV__ENET_RX_EN,

MX6Q_PAD_ENET_TXD0__ENET_TDATA_0,

MX6Q_PAD_ENET_TXD1__ENET_TDATA_1,

MX6Q_PAD_ENET_TX_EN__ENET_TX_EN,

MX6Q_PAD_GPIO_16__ENET_ANATOP_ETHERNET_REF_OUT,

MX6Q_PAD_ENET_RX_ER__ENET_RX_ER,

-------------------------------------------------------------------------

My fec init procedure:

board_mx6q_XXX.c file

----------------------------------------------------------------------

static int mx6q_8720_fec_phy_init(struct phy_device *phydev)

{

int val;

mxc_iomux_set_gpr_register(1, 21, 1, 1);

/* reset phy */

val = phy_read(phydev, 0x0);

phy_write(phydev, 0x0, (val |BMCR_RESET));

msleep(10);

val = phy_read(phydev, 0x0);

if (val & BMCR_PDOWN) {

phy_write(phydev, 0x0, (val & ~BMCR_PDOWN));

}

return 0;

}

--------------------------------------------------------

Please give me a suggestion or idea.

B&R

peter.cao

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi all,

i have solved the problem.

the crash problem is If no phy detect, i open the eth interface, it is not reasonable.

the cause that no phy detected when power-on is the sending phy clk is after phy detect.

so i manually enable enet_clk at mx6_clocks_init() , and the problem is solved.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Could you share the code that how to fixed this issue?

thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

could you share the code that how to fixed this issue?thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

during debug, i found the following log error:

eth0: no PHY, assuming direct connection to switch

PHY 0:00 not found

eth0: could not attach to PHY

IP-Config: Failed to open eth0

IP-Config: No network devices available.

i traced the code and found it does not find the attached phy in fep->mii_bus->phy_map in fec_enet_mii_probe function (fec.c),

the map is null.

do anyone know why the map is null?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi fang

I think that connection nRST to POR is not good.

Because LAN8720 VDD1A,VDD2A,VDDIO are turned ON

later in software, such configuration is used on Freescale designs.

Probably for that reason you see "PHY not found" error.

Actually you can check with SDK LAN8720 example, if processor can

detect PHY.

"MX6_PLATFORM_SDK "

Best regards

chip

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi, chipexpert

my link led has lighted and it can find out phy and got ip.

but now i encounter a new problem.

when the power on, it can not find out phy . and when i input the "ifconfig eth0 up", the kernel dumped.

but when i input reboot cmd, it can find out phy and got ip after reboot.

i trace the source and found it hangs on napi_enable(&fep->napi);; in fec_enet_open function (fec.c)

how to fix it?

----------------------------------------------------------------------------------------------

kernel BUG at include/linux/netdevice.h:520!

Unable to handle kernel NULL pointer dereference at virtual address 00000000

pgd = b29f4000

[00000000] *pgd=429c5831, *pte=00000000, *ppte=00000000

Internal error: Oops: 817 [#1] PREEMPT SMP

Modules linked in:

CPU: 1 Not tainted (3.0.35 #28)

PC is at __bug+0x1c/0x28

LR is at __bug+0x18/0x28

pc : [<8004068c>] lr : [<80040688>] psr: 40000013

sp : b28b1df0 ip : 80035f40 fp : 00000000

r10: b22a8fc0 r9 : 00000000 r8 : b21abf0c

r7 : b201b044 r6 : 00000000 r5 : b201b000 r4 : b201b000

r3 : 00000000 r2 : 00000001 r1 : 80a75d18 r0 : 00000033

Segmentation faultFlags: nZcv IRQs on FIQs on Mode SVC_32 ISA ARM Segment user

Control: 10c53c7d Table: 429f404a DAC: 00000015

..........

[<8004068c>] (__bug+0x1c/0x28) from [<802f83d8>] (fec_enet_open+0x3b8/0x480)

[<802f83d8>] (fec_enet_open+0x3b8/0x480) from [<80422868>] (__dev_open+0xa0/0xf0)

[<80422868>] (__dev_open+0xa0/0xf0) from [<80422a90>] (__dev_change_flags+0x7c/0x134)

[<80422a90>] (__dev_change_flags+0x7c/0x134) from [<80422bb4>] (dev_change_flags+0x10/0x48)

[<80422bb4>] (dev_change_flags+0x10/0x48) from [<80474a1c>] (devinet_ioctl+0x77c/0x818)

[<80474a1c>] (devinet_ioctl+0x77c/0x818) from [<8040e844>] (sock_ioctl+0x68/0x260)

[<8040e844>] (sock_ioctl+0x68/0x260) from [<800fc0a0>] (do_vfs_ioctl+0x80/0x54c)

[<800fc0a0>] (do_vfs_ioctl+0x80/0x54c) from [<800fc5a4>] (sys_ioctl+0x38/0x5c)

[<800fc5a4>] (sys_ioctl+0x38/0x5c) from [<8003d000>] (ret_fast_syscall+0x0/0x30)

Code: e59f0010 e1a01003 eb1321bd e3a03000 (e5833000)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi pfsang

I'm not sure but try this fix

arch/arm/mach-mx6/clock.c

int __init mx6_clocks_init(unsigned long ckil, unsigned long osc,

unsigned long ckih1, unsigned long ckih2)

{

....

- - pll8_enet_main_clk.disable(&pll8_enet_main_clk);

++ pll8_enet_main_clk.enable(&pll8_enet_main_clk);

Alexander

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi,

i made a mistake about the bug. the bug is not at clk_enable , is at i napi_enable(&fep->napi)( fec_enet_open ). do you know why it will crash?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi fang min

I think GPR1 register must be set before imx6_init_fec()

static void __init xxx_board_init(void)

{

...

++ mxc_iomux_set_gpr_register(1, 21, 1, 1);

imx6_init_fec(fec_data);

not in function

static int mx6q_8720_fec_phy_init(struct phy_device *phydev)

{

int val;

-- mxc_iomux_set_gpr_register(1, 21, 1, 1);

as in your example

Alexander

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi Alexander

thank you for your reply. i will try it tomorrow

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi fang

nRST is hardware reset and this signal latches hardware LAN8720 configuration

(MODE[] signals), seems it is not possible to set it with software reset.

I would suggest to apply to LAN8720 vendor (SMSC) tech

support for workaround.

Best regards

chip

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi, chipexpert

we connect nRst pin with POR_B , which is global reset. when power on, pmic willl reset imx6 and others peripherals included lan8720a. seems i needn't to set it with soft reset .

is that right ?