- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- iMX8M Mini Use PI6CFGL201BZDIEX as PCIe REF_CLK

iMX8M Mini Use PI6CFGL201BZDIEX as PCIe REF_CLK

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

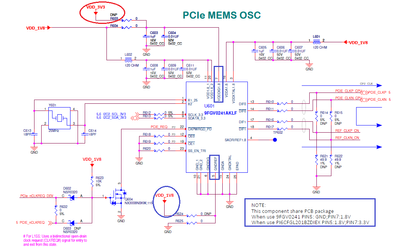

Following reference design, we are making custom board with iMX8M Mini but replace the default PCIe clock generator (9FGV0241AKLF) with PI6CFGL201BZDIEX.

Also, a related post https://community.nxp.com/t5/i-MX-Processors/iMX8M-Mini-CLK-Generator-Clocking-Issue/m-p/1258056 indicates that PI6CFGL201BZDIEX can be used.

However, when it is replaced with PI6CFGL201BZDIEX, the driver (imx6q-pcie) will panic after reporting "PLL lock timeout". Then, kernel gets stuck and just hangs.

[ 2.677860] imx6q-pcie 33800000.pcie: EXT REF_CLK is used!.

[ 2.734722] imx6q-pcie 33800000.pcie: PCIe PLL lock timeout

Is there any driver change needed for the driver (drivers/pci/controller/dwc/pci-imx6.c )? Or, we need to change the DTS because of the replacement?

Thanks,

Weichen

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi weidong_sun,

We tried to put the PCI module to M.2 and it worked. Like you mentioned, it seems that M.2 side of channel is working but the CPU-side doesn't. We are still investigating why it acts like this.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

these 2 clock generators are pin to pin compatible, but PIN7 and PIN5 are different definitions.

--The clock generator can output 2-channel 100MHz clocks, one channel is for CPU side, the other is for M.2 connector.

--The clock generator doesn't need linux driver, default configuration is OK.

So now you can measure whether 100MHz clock OUPUT or not.

According to your description, obviously, CPU side doesn't get the clock input or bad clock waveform.

Have a nice day!

B.R,

weidong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi weidong_sun,

We tried to put the PCI module to M.2 and it worked. Like you mentioned, it seems that M.2 side of channel is working but the CPU-side doesn't. We are still investigating why it acts like this.