- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Question about FREQ1/2 setpoint Clock Cycle Freq of DDR Register Programming Aid

Question about FREQ1/2 setpoint Clock Cycle Freq of DDR Register Programming Aid

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I have a question about FREQ1/2 setpoint Clock Cycle Freq of DDR Register Programming Aid which can be downloaded from following link.

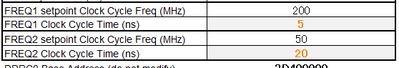

According to description for sheet, the settings are fixed as below in the sheet.

I wondered if FREQ1 and FREQ2 depend on frequency rather than fixed values.

Q1.

What is this value (200MHz, 50MHz) based on?

Q2.

Can you tell me why this value can be a fixed value?

Ko-hey

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@ko-hey

Look at section " Dynamic Bus Frequency" in "i.MX_Reference_Manual.pdf".

Yes, it may be recommended to not modify it.

~Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@ko-hey

Hello,

Those working points are used by NXP Linux with CPUFREQ and Dynamic

Bus Frequency features.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for reply.

Which source code does the setpoint use ?

Is it recommended to use it unchanged ?

Ko-hey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@ko-hey

Look at section " Dynamic Bus Frequency" in "i.MX_Reference_Manual.pdf".

Yes, it may be recommended to not modify it.

~Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to Table 16. BusFrequency Set Points, i.MX 8M had a DDRC APB clock of 200MHz.

FREQ1 setpoint Clock cycle Freq (C31 cell, 200MHz) in the Register Configuration sheet refers to the DDRC APB clock.

Is my understanding correct?

On the other hand, the clock corresponding to FREQ2 setpoint clock cycle freq (C33 cell, 50MHz) was not described in the above pdf.

Which clock does the 50MHz clock refer to ?

ko-hey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@ko-hey

Hello,

"Although there are three frequency points in the BSP and RPA tool including ~1500MHz/200MHz/50MHz, we only use the highest frequency and the lowest frequency 50MHz(FREQ2) in the BSP."

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content