- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

MDIO timing on i.MX6SX

Hi community,

I have a question about i.MX6SX Ethernet.

In IMX6SXCEC.pdf, 4.12.6.1.4 MII Serial Management Channel Timing(ENET_MDIO and ENET_MDC),

ENET_MDIO output change at the falling edge of ENET_MDC.

But, I measured with an actual device,

ENET_MDIO output changed at the rising edge of ENET_MDC.

Why is the result different from the data sheet?

Best Regards,

Hiroshi Katagiri

Hello,

I think the main problem is, that terminology and approach of the Serial Management Interface specification in the IEEE 802.3 standard are not the same as NXP (Freescale) uses regarding MDC / MDIO specs.

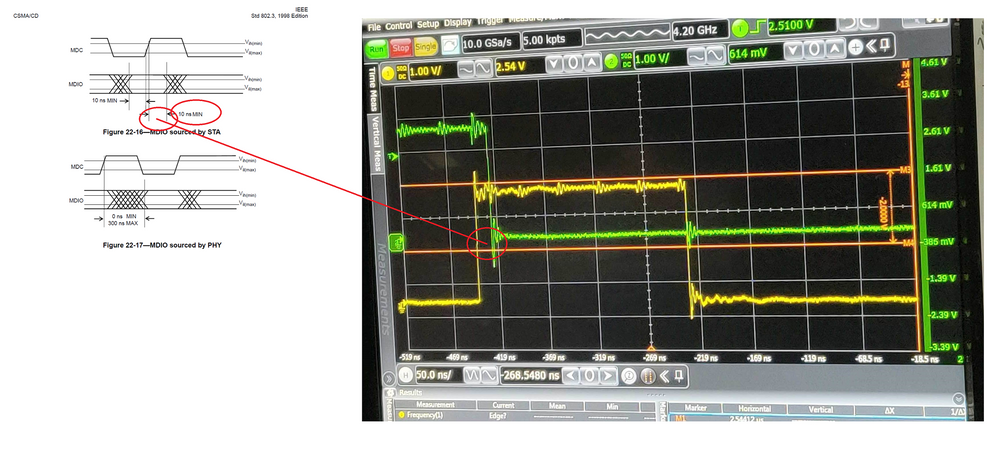

According to IEEE 802.3: “When the STA sources the MDIO signal, the STA shall providea minimum of 10 ns of setup time and a minimum of 10 ns of hold time referenced to the rising edge of MDC, [...] measured at the MII connector.” Here i.MX6 ENET (STA) output is considered. For outputs NXP i.MX documentation does not use terms setup and hold: it operates with delays, and delays are measured relative other / non-active edge. For MII Serial Management it corresponds falling edge, assuming rising edge is active.

According to IEEE 802.3: “When the MDIO signal is sourced by the PHY, it is sampled by the STA synchronously with respect to the rising edge of MDC. The clock to output delay from the PHY, as measured at the MII connector, shall be a minimum of 0 ns, and a maximum of 300 ns...”. Here the PHY is output, so i.MX6 ENET is input. Setup and hold timings (not delays as in IEEE 802.3) relative active edge are used in NXP i.MX documentation.

Regards,

Yuri.

Actually, the M10 and M11 parameters the i.MX6 Data Sheet document specifies are not the MDIO output Setup and Hold times. These parameters are internal to the processor and are not related with the Serial Management Interface specification of the IEEE 802.3 standard. The data change point timing is not defined in the IEEE 802.3 standard, the only definition is minimum 10ns of Setup and Hold time of the MDIO output signal with regard to the rising edge of MDC. In that meaning, the MDC and MDIO signals of the processor are compliant with the IEEE 802.3 standard.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi all,

I have the same doubt as Hiroshi Katagiri. My PHY samples the data received from the MAC (STA or iMX) on the rising edge of the MDC. I see the same waveform posted by Hiroshi, where it seems that the MAC changes MDIO on the rising edge of MDC.

Does this mean that the STA (i.MX) keeps MDIO stable for 10ns after the clock is switched to '1'?

And in the opposite direction, reading by iMX: my PHY drives MDIO changing on the rising edge of MDC, with a minimum 0ns delay.

Does iMX sample MDIO on falling or rising edges? (My PHY doesn't guarantee 10ns of hold, in case imx samples on rising edge of MDC. )

Thank you very much.

Best regards,

Elena

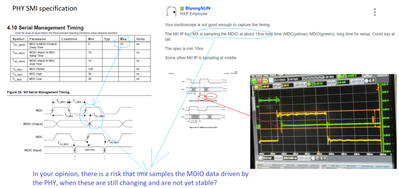

Your oscilloscope is not good enough to capture the timing.

The MII IP for i.MX is sampling the MDIO at about 15ns hold time (MDC(yellow), MDIO(green)). long time for setup. Could say at tail.

The spec is min 10ns

Some other MII IP is sampling at middle.

When you read the i.MX6SX, please make sure you understand the input/output corresponding to the spec sourced by STA or sourced by PHY.

BTW,the waveform is same for i.MX6 family, actually it is from i.MX6SX.

That is why in my reply

"When you read the i.MX6SX, please make sure you understand the input/output corresponding to the spec sourced by STA or sourced by PHY."

and where is the waveform pointed to the figure in spec picture.

it is "sourced by". it is not you are tx and i am rx.

"sourced by" is you should use "this" I provide.

It is not a uart. It is similar to the i2c. it is one clock and one data line. each one use the same wave form to get data.

your question seems like use the difference waveform in one session.

my example is i.MX6SX to PHY or PHY to i.MX6SX? what is i.MX6SX and PHY doing at that time.

I leave this question for you to answer.