- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: MCIMX6S5DVM10AB EOL in 2020

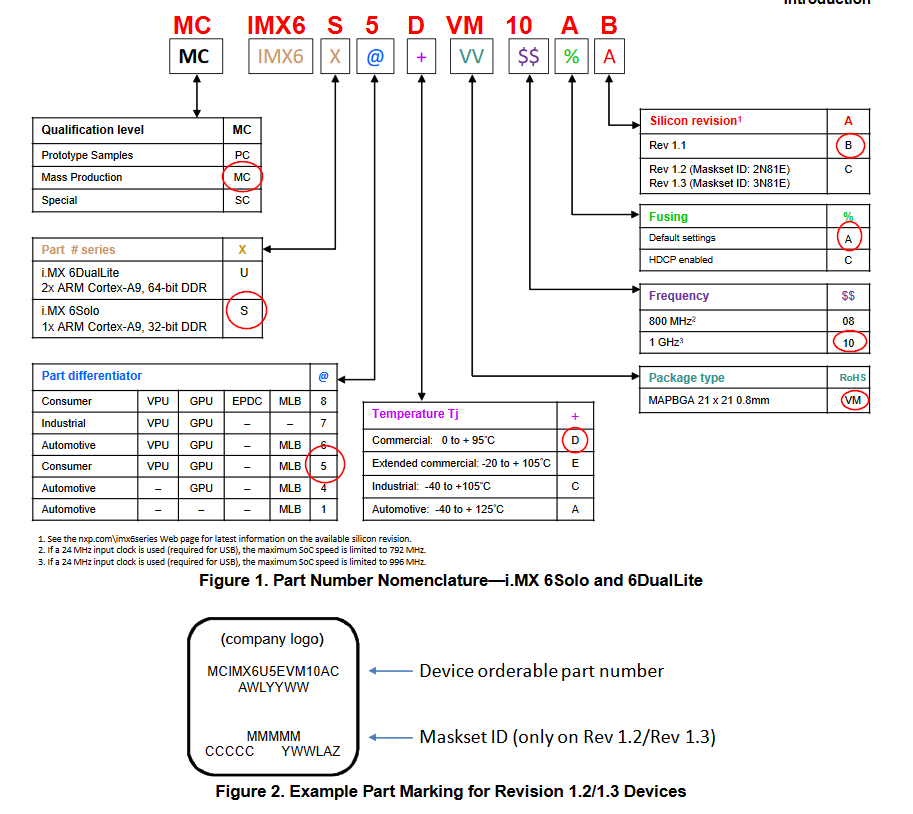

MCIMX6S5DVM10AB EOL in 2020

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

i noticed that MCIMX6S5DVM10AB is going EOL in 2020. One possible alternative would be MCIMX6S8DVM10AD, but I can't find a detailed comparison between them. For instance, does the S8 have same peripheral that S5 have? I don't mind if there is something added in the S8. Will there a porting of drivers be needed?

I could find is that MCIMX6S8DVM10AD has a new silicon revision and additional EPDC.

Simple question would be what this alternative means for the SW PoV and what for the HW PoV. Or is there any other alternative to MCIMX6S5DVM10AB which would add little to no extra work for the transition.

Thanks in advance for any help,

Vasja

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Vasja,

You may use MCIMX6S8DVM10AD as a replacement. The main difference in terms of features is as you mentioned the updated silicon revision to 1.4 and the addition of EPDC.

The EPDC should cause no problem as you wouldn’t be using it.

As for the silicon revision you are using revision 1.1 you would need to review these changes even if using a processor with the same features, as all parts being produced are the newest silicon revision. These changes should not greatly affect your design but it’s important to review them. They are available on the Engineering Bulletin 804 (link below)

https://www.nxp.com/docs/en/engineering-bulletin/EB804.pdf

The changes in revision 1.4 are the inclusion of some fuses that allow to force an internal boot to prevent tampering with the BOOT_MODE pins, which is recommended for security-enabled applications.

I hope this helps!

Regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Vasja,

You may use MCIMX6S8DVM10AD as a replacement. The main difference in terms of features is as you mentioned the updated silicon revision to 1.4 and the addition of EPDC.

The EPDC should cause no problem as you wouldn’t be using it.

As for the silicon revision you are using revision 1.1 you would need to review these changes even if using a processor with the same features, as all parts being produced are the newest silicon revision. These changes should not greatly affect your design but it’s important to review them. They are available on the Engineering Bulletin 804 (link below)

https://www.nxp.com/docs/en/engineering-bulletin/EB804.pdf

The changes in revision 1.4 are the inclusion of some fuses that allow to force an internal boot to prevent tampering with the BOOT_MODE pins, which is recommended for security-enabled applications.

I hope this helps!

Regards,