- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: MCIMX6Q-SDB ECSPI signal control

MCIMX6Q-SDB ECSPI signal control

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MCIMX6Q-SDB ECSPI signal control

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

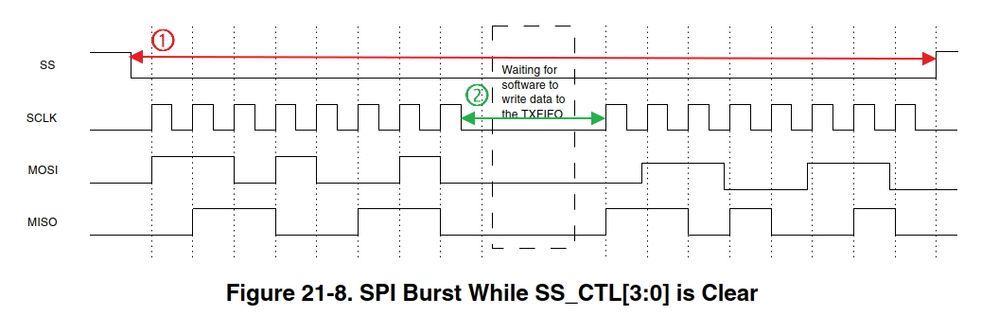

目標 : 控制 i.MX6-SDB ECSPI1 port 輸出如附件一波形,並且符合兩個控制條件,① 控制一個 SS 信號傳送 Byte 數,② 控制兩個 Byte 之間延遲時間。

1. 軟體 (BSP 設定):

(1) 如附件二圖在 Device Drivers / SPI support / Freescale DSPI controller 設定 built-in。

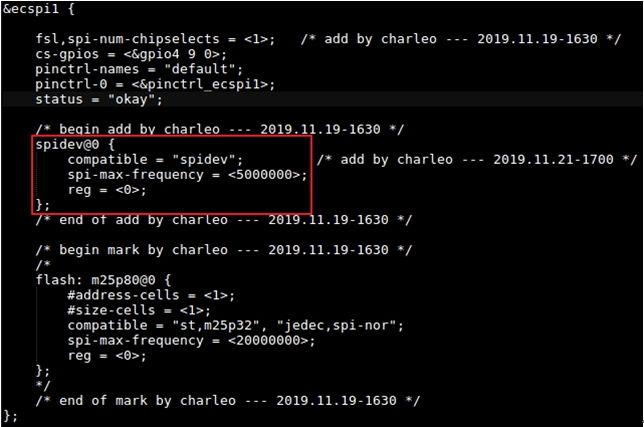

(2) DTS (/tmp/work/imx6qsabresd-poky-linux-gnueabi/linux-imx/4.14.98-r0/git/arch/arm/boot/dts/imx6qdl-sabresd.dtsi)

修改兩個地方如附件三和附件四。

a.

spidev@0 {

compatible = "spidev"; /* add by charleo --- 2019.11.21-1700 */

spi-max-frequency = <5000000>;

reg = <0>;

};

b.

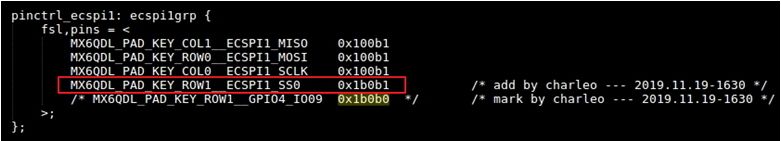

pinctrl_ecspi1: ecspi1grp {

fsl,pins = <

MX6QDL_PAD_KEY_COL1__ECSPI1_MISO 0x100b1

MX6QDL_PAD_KEY_ROW0__ECSPI1_MOSI 0x100b1

MX6QDL_PAD_KEY_COL0__ECSPI1_SCLK 0x100b1

MX6QDL_PAD_KEY_ROW1__ECSPI1_SS0 0x1b0b1 /* add by charleo --- 2019.11.19-1630 */

/* MX6QDL_PAD_KEY_ROW1__GPIO4_IO09 0x1b0b0 */ /* mark by charleo --- 2019.11.19-1630 */

>;

};

2. 使用 ls /dev/ 命令,確認 spidev0.0 裝置已產生,如附件五。

3. debug port 輸入 echo "h" >> /dev/spidev0.0 輸出波型如附件六。

4. 嘗試使用 memtool 設定 ECSPI1.PERIODREG.SAMPLE_PERIOD 和 ECSPI1.CONREG.BURST_LENGTH 參數都無法達到目標,請問是否有哪裡設定錯誤,或建議可以解決,謝謝大家。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can change the SS signal to GPIO. So, you can control the SS output by yourself.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jimmy,

It still the same issue in i.MX8Mmini CPU. (Base on BSP version 4.14.98_200 , 4.14_98_210)