- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Working on custom board with the imx6dqscm and we are trying to communicate with a ksz8795 switch through SPI. We have worked with a couple of drivers listed below:

http://lxr.free-electrons.com/source/drivers/net/phy/spi_ks8995.c

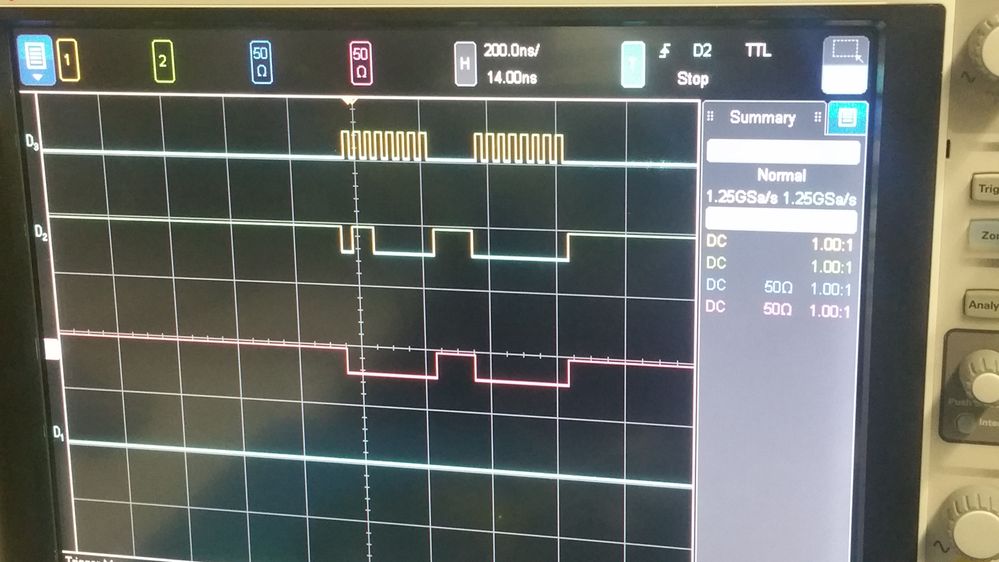

Everything seems to be configured correctly because we can see the correct clock signals and MOSI data going into the ksz8795. The only issue is that we are noticing that the chip select line is toggling between packets. We are thinking that this is terminating communication between the imx6 and the switch. I've looked in the RM and saw that there might be a potential wait state creating that delay, but I've checked that register and found 0 wait states. I am not sure what is causing the chip select to go high between packets. My questions are, what is causing this delay and how can I modify the driver to keep the SS low? I am just a little skeptical because these drivers are specific for this device, therefore, I must be missing something trivial.

已解决! 转到解答。

Turns out that using ECSPI3_SS0 to drive the chip select line generates the wait state between bursts. Instead, we define cs-gpios to an I/O pin and the driver kept the slave select low between bursts. Also, we used the driver provided by microchip.

Hi Ali

by definition of spi protocol signal SS is toggling on every burst

according to sect.21.4.4.1 Typical Master Mode i.MX6DQ Reference Manual

and setting ECSPIx_CONREG[BURST_LENGTH]

http://cache.freescale.com/files/32bit/doc/ref_manual/IMX6DQRM.pdf

If permanent ss low is needed, one can configure it as gpio setting low

level in spi probe function.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Igor,

If you take a look at section 21.4.4.1.3, figure 21-8 is really what I need. The SS line is low between sending bursts and the burst length in that case is 8. I do not have any wait states so I am not sure why the SS line is going high between those two bursts.

Turns out that using ECSPI3_SS0 to drive the chip select line generates the wait state between bursts. Instead, we define cs-gpios to an I/O pin and the driver kept the slave select low between bursts. Also, we used the driver provided by microchip.