- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- IMX6UL Linux/OPTEE Increasing RAM

IMX6UL Linux/OPTEE Increasing RAM

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

IMX6UL Linux/OPTEE Increasing RAM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

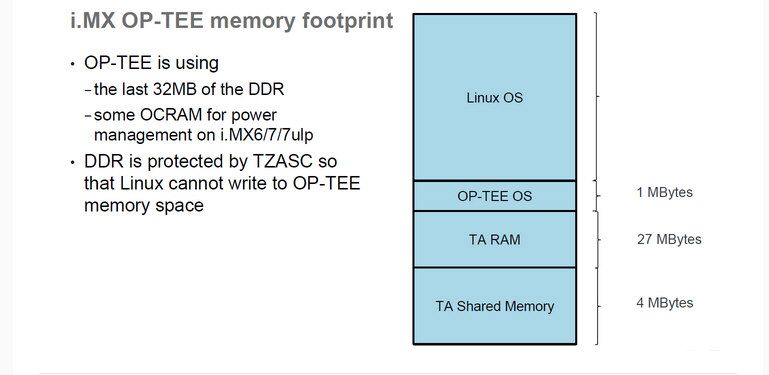

I'm trying to get my board to recognise all my RAM, I had it recognising 128MB but I have 1GB installed. I have used the DDR configuration tool to configure uboot to configure the memory registers and it recognises the full amount of RAM. I can load an image onto the board using UUU, but on a restart I get the message "Starting kernel ..." from uBoot, then a few messages from OP-TEE starting, then the whole system hangs. From booting without my mods, I'd expect to get "Booting Linux on physical CPU 0x0". I have also CFG_DDR_SIZE in OP-TEE to 0x40000000.

What else do I need to configure?

Here is my memory configuration in uboot:

//=============================================================================

// Calibration setup.

//=============================================================================

DATA 4 0x021b0800 0xA1390003 // DDR_PHY_P0_MPZQHWCTRL, enable both one-time & periodic HW ZQ calibration.

// For target board, may need to run write leveling calibration to fine tune these settings.

DATA 4 0x021b080c 0x000E0000

//Read DQS Gating calibration

DATA 4 0x021b083c 0x01480150 // MPDGCTRL0 PHY0

DATA 4 0x021b0840 0x00000000 // MPDGCTRL1 PHY0

//Read calibration

DATA 4 0x021b0848 0x40404E50 // MPRDDLCTL PHY0

//Write calibration

DATA 4 0x021b0850 0x40405048 // MPWRDLCTL PHY0

//read data bit delay: (3 is the reccommended default value, although out of reset value is 0)

DATA 4 0x021b081c 0x33333333 // MMDC_MPRDDQBY0DL

DATA 4 0x021b0820 0x33333333 // MMDC_MPRDDQBY1DL

//write data bit delay:

DATA 4 0x021b082c 0xF3333333 // MMDC_MPWRDQBY0DL

DATA 4 0x021b0830 0xF3333333 // MMDC_MPWRDQBY1DL

//DQS&CLK Duty Cycle

DATA 4 0x021b08c0 0x00921012 // [MMDC_MPDCCR] MMDC Duty Cycle Control Register

// Complete calibration by forced measurement:

DATA 4 0x021b08b8 0x00000800 // DDR_PHY_P0_MPMUR0, frc_msr

//=============================================================================

// Calibration setup end

//=============================================================================

//MMDC init:

DATA 4 0x021b0004 0x0002002D // MMDC0_MDPDC

DATA 4 0x021b0008 0x1B333030 // MMDC0_MDOTC

DATA 4 0x021b000c 0x8B8F5333 // MMDC0_MDCFG0

DATA 4 0x021b0010 0xB68E0B63 // MMDC0_MDCFG1

DATA 4 0x021b0014 0x01FF00DB // MMDC0_MDCFG2

//MDMISC: RALAT kept to the high level of 5.

//MDMISC: consider reducing RALAT if your 528MHz board design allow that. Lower RALAT benefits:

//a. better operation at low frequency, for LPDDR2 freq < 100MHz, change RALAT to 3

//b. Small performence improvment

DATA 4 0x021b0018 0x00211740 // MMDC0_MDMISC

DATA 4 0x021b001c 0x00008000 // MMDC0_MDSCR, set the Configuration request bit during MMDC set up

DATA 4 0x021b002c 0x000026D2 // MMDC0_MDRWD

DATA 4 0x021b0030 0x008F1023 // MMDC0_MDOR

DATA 4 0x021b0040 0x0000005F // Chan0 CS0_END

DATA 4 0x021b0000 0x85180000 // MMDC0_MDCTL

DATA 4 0x021b0890 0x00400a38 // MPPDCMPR2

//Mode register writes

DATA 4 0x021b001c 0x02008032 // MMDC0_MDSCR, MR2 write, CS0

DATA 4 0x021b001c 0x00008033 // MMDC0_MDSCR, MR3 write, CS0

DATA 4 0x021b001c 0x00048031 // MMDC0_MDSCR, MR1 write, CS0

DATA 4 0x021b001c 0x15208030 // MMDC0_MDSCR, MR0write, CS0

DATA 4 0x021b001c 0x04008040 // MMDC0_MDSCR, ZQ calibration command sent to device on CS0

DATA 4 0x021b0020 0x00007800 // MMDC0_MDREF

DATA 4 0x021b0818 0x00000227 // DDR_PHY_P0_MPODTCTRL

DATA 4 0x021b0004 0x0002556D // MMDC0_MDPDC now SDCTL power down enabled

DATA 4 0x021b0404 0x00011006 // MMDC0_MAPSR ADOPT power down enabled, MMDC will enter automatically to self-refresh while the number of idle cycle reached.

DATA 4 0x021b001c 0x00000000 // MMDC0_MDSCR, clear this register (especially the configuration bit as initialization is complete)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Nick

one can try to boot without optee, in particular memory size can be adjusted

in uboot with #define PHYS_SDRAM_SIZE

mx6ul_14x14_evk.h\configs\include - uboot-imx - i.MX U-Boot

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

I have set PHYS_SDRAM_SIZE to SZ_1G with no luck, I have the exact same problem.

I believe it does boot with if I disable OP-TEE, I need to use OP-TEE for my application though.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Nick

also one can look at similar issue on

Hikey 620: increase TA RAM in OP-TEE · Issue #2313 · OP-TEE/optee_os · GitHub

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

I have solved this issue by pulling the latest version of imx-optee-os.

Evidently, this was solved in the last few months.

Thanks for your help.