- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

How to trigger software interrupt from iMX8 A35 to M4

Hello,

I need to trigger a user define software interrupt from Cortex A35 to Cortex M4 in IMX8 board. Please advice.

Linux 4.14.98 is running in A35.

Best regards,

Praveen

Hi Praveen

for available options one can look at Chapter 10

RPC Protocol, "Interrupts" System Controller Firmware API Reference Guide

included in SCFW Porting Kit

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Thanks Igor for quick response.

Do you mean that I can use sc_irq_enable() to generate the interrupt at A35 and sc_irq_status() to read the IRQ value at M4?

Since SCU APIs are kernel library in Linux; do you have any suggestion on how to use it from user space?

Thanks and regards,

Praveen

I am not sure that it is possible to implement that using SCU APIs,

you can find some examples in SDK_MEK-MIMX8QM

Welcome | MCUXpresso SDK Builder

In any way there are no other options for interaction between cores except SCU APIs.

Best regards

igor

Hi Igor,

As per my understanding, to access kernel library we shall create a driver / procfs / sysfs.

What we wanted to be sure that does NXP provides SCU driver for Linux or any procfs file, which can be used to access SCU APIs?

Is there any example in Linux OS, where application is using SCU APIs?

Best regards,

Praveen

Hi Praveen

please read documentation included in SCFW Porting Kit ,

in particular sc_fw_api.pdf

>Is there any example in Linux OS, where application is using SCU APIs?

ipc.c\main\sc\imx\soc\drivers - linux-imx - i.MX Linux kernel

check also sect.2.2 System Controller Linux Manual in Linux 4.19.35_1.1.0 Documentation

Best regards

igor

Hi Igor,

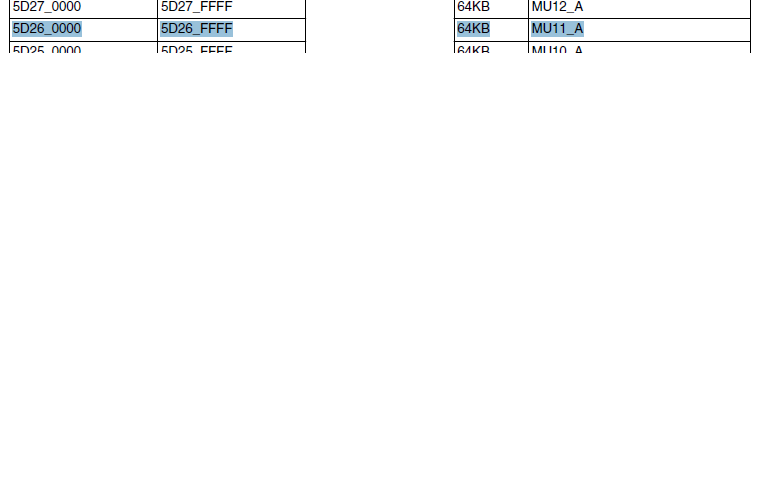

If LSIO #13 MU is used to interrupt M4 from A35 and visa-versa, then where shall in the BSP and M4 code, the config changes be made? And what those changes will be? Will INTMUXC and INT-Steer (and its mapping to M4-NVIC) also gets impacted?

Best regards,

Praveen

Hello Igor,

Waiting for your response for the above queries.

Further to that I have couple of more query:

- Per the Table 2.4 of IMX8 Reference Manual, the size of MU11_A is 64KB; Per section 12.9.4 there are 4 Tx, 4 Rx, 1 Status and 1 Control Registers of 32bits. Register size is just 40 bytes, the rest of the memory is used for what?

2. Why NVIC is only in Cortex M4 and SCU?

Best regards,

Praveen

Hello Igor,

I agree with you; using SCU APIs may not help in this case.

We are planning to use MU11_A and MU11_B for interrupt generation from A35 to M4. In this approach, we seek your support on what all we shall take care.

Best regards,

Praveen

Hi Praveen,

I am interested in implementing a similar use case where M4 signal A35 cores by issuing a remore interrupt, and the same in opposite direction.

Did you finally experiment it ?

Could you give some feedback ?

Thanks in advance,

Best Regards,

Laurent