- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- How to run M7 code from both TCM and DDR?

How to run M7 code from both TCM and DDR?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

How to run M7 code from both TCM and DDR?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

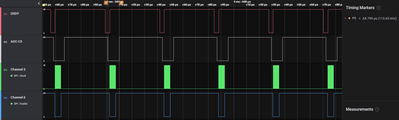

I have a simple program running on the M7 (i.MX8 Nano) which triggers a GPIO interrupt to unblock the SPI read when a "data ready" signal is received from the ADC ~every 43us.

When I run this code in TCM, timing looks great and everything works beautifully.

Note: "ADC CS" is a separate GPIO pin that complements the native SPI Chip Select to select one of multiple SPI slaves in the SPI bus.

When I run the code from DDR, the ISR was not serviced timely and the entire routine to retrieve the SPI data takes about 10 times longer! Is there a way to speed up the code running from the DDR?

How to setup the code to run from both TCM and DDR?

Due to the size of the TCM (128K each for Instructions and Data), running our entire program on the TCM is not a viable solution, I read that it is possible to run the most time critical routines (ISR, real time tasks) from the TCM and the rest from the DDR. Is there an example somewhere that I can refer to see how this is done?

Any pointers on how to address the execution speed limitation is greatly appreciated. Thanks!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @jpsk,

[Q] Is there a way to speed up the code running from the DDR?

[A]

The biggest factor is cache! You must enable the M4 cache when running from DDR.

That will help you speed up the code running.

Best Regards,

Dhruvit.